# TECHNISCHE UNIVERSITÄT CHEMNITZ

MASTER THESIS

# On-Board Memory Extension on Reconfigurable Integrated Circuits using External DDR3 Memory

Submitted by

## Bhaveen Lodaya

(353988)

for the fulfilment of the academic degree

Master of Science in Automotive Software Engineering Technische Universität Chemnitz

## Supervisor:

#### Prof. Dr. Wolfram Hardt

Department of Computer Science, Technische Universität Chemnitz, Germany.

#### Advisor:

## Dipl.-Ing. Stephan Blokzyl

Department of Computer Science, Technische Universität Chemnitz, Germany.

# Aufgabenstellung

zur

Abschlussarbeit im Studiengang Master Automotive Software Engineering

für

Herrn Bhaveen Lodaya geb. am 14. Mai 1990 in Dombivli, Thane

zum Thema

On-board Memory Extension on Reconfigurable Integrated Circuits using External DDR3 Memory

Betreuer/ Prüfer:

Prof. Dr. Wolfram Hardt

Ausgabedatum:

09.06.2016

Abgabedatum:

17.11.2016

Tag der Abgabe:

Unterschrift:

Prof. Dr. F. Hamker

Vorsitzender des Prüfungsausschusses

# Acknowledgement

I would like to extend my sincere gratitude to all the people who were involved in helping me make this master thesis a success.

I am very thankful to Prof. Dr. Wolfram Hardt for providing me with an opportunity to work on master thesis under his professorship.

A special gratitude I give to my advisor and mentor, Dipl.-Ing. Stephan Blokzyl, whose contribution in the form of his involvement in long discussions, experienced suggestions, constant encouragement and guidance has helped me get through my problems and difficulties.

Furthermore, I would also like to acknowledge the help provided by the other staff members of the Computer Science department by providing me with the tools, equipment and a quiet and peaceful place to work.

I take this opportunity to express my appreciation to my family and friends who have provided me with continuous moral support during the course of the thesis.

# **Abstract**

User-programmable, integrated circuits (ICs) e.g. Field Programmable Gate Arrays (FPGAs) are increasingly popular for embedded, high-performance data exploitation. They combine the parallelization capability and processing power of application specific integrated circuits (ASICs) with the flexibility, scalability and adaptability of software-based processing solutions. FPGAs provide powerful processing resources due to an optimal adaptation to the target application and a well-balanced ratio of performance, efficiency and parallelization.

One drawback of FPGA-based data exploitation is the limited memory capacity of reconfigurable integrated circuits. Large-scale Digital Signal Processor (DSP) FP-GAs provide approximately 4MB on-board random access memory (RAM) which is not sufficient to buffer the broadband sensor and result data. Hence, additional external memory is connected to the FPGA to increase on-board storage capacities.

External memory devices like double data rate three synchronous dynamic random access memories (DDR3-SDRAM) provide very fast and wide bandwidth interfaces that represent a bottleneck when used in highly parallelized processing architectures. Independent processing modules are demanding concurrent read and write access.

Within the master thesis, a concept for the integration of an external DDR3-SDRAM into an FPGA-based parallelized processing architecture is developed and implemented. The solution realizes time division multiple access (TDMA) to the external memory and virtual, low-latency memory extension to the on-board buffer capabilities. The integration of the external RAM does not change the way how on-board buffers are used (control, data-flow).

# **Contents**

| Ac  | knov                                | vledgement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii                        |

|-----|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Αŀ  | ostrac                              | ct Control of the Con | iv                         |

| Lis | st of                               | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | viii                       |

| Lis | st of                               | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X                          |

| Lis | st of                               | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | хi                         |

| 1.  | 1.1.                                | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>1<br>3                |

| 2.  | Stat                                | e of the Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                          |

|     | <ul><li>2.1.</li><li>2.2.</li></ul> | Memory management to support multitasking on FPGA-based systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4<br>4<br>5<br>6<br>7<br>8 |

|     | 2.3.                                | 2.2.2. Instruction decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10<br>10<br>10             |

|     | 2.4.<br>2.5.                        | Caching techniques in x86 processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12<br>13                   |

| 3.  | Con                                 | cept, Design and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                         |

|     | 3.1.<br>3.2.                        | 8 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>17<br>18<br>18<br>19 |

|     | 3.3.                                | Common WRITE 2 FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                         |

|            | 3.4.   | Data-flow controller                            | 21              |

|------------|--------|-------------------------------------------------|-----------------|

|            |        | 3.4.1. Data-flow controller master              | 21              |

|            |        | 3.4.2. Data-flow controller slave               | 22              |

|            | 3.5.   | Memory interface generator controller           | 24              |

|            | 3.6.   | Generic multiplexer                             | 27              |

| 1          | Pool   | ization                                         | 29              |

| 4.         |        | Hardware                                        |                 |

|            | 4.1.   | 4.1.1. Virtex-6                                 |                 |

|            |        |                                                 | 29<br>29        |

|            |        |                                                 | 31              |

|            | 4.2.   |                                                 | 31              |

|            | 1.2.   |                                                 | 31              |

|            |        | <u> </u>                                        | 31              |

|            |        | <u> </u>                                        | 32              |

|            | 4.3.   | 8                                               | 32              |

|            | 1.0.   | 1 1 0                                           | 32              |

|            |        |                                                 | 34              |

|            |        | 4.3.3. Memory interface generator               |                 |

| <b>E</b>   | Eval   | uation and Validation                           | 44              |

| J.         | 5.1.   |                                                 |                 |

|            | 5.2.   |                                                 | 45              |

|            | 5.3.   | 9                                               | 47              |

|            | 5.4.   | 88                                              | $\frac{1}{47}$  |

|            | 5.5.   |                                                 | <br>48          |

|            | 5.6.   | 1 0                                             | $\frac{-0}{49}$ |

|            | 5.7.   |                                                 | 52              |

|            | 5.8.   |                                                 | 52              |

| _          | _      |                                                 | - 4             |

| <b>b</b> . |        |                                                 | 54              |

|            | •      |                                                 | 55<br>          |

|            | 0.2.   | Future work                                     | 55              |

| Bi         | bliogi | raphy !                                         | 57              |

| Αp         | pend   | lices                                           | 60              |

| _          |        |                                                 | c 1             |

| Α.         |        | •                                               | 61<br>61        |

|            |        | S 1                                             | 61<br>61        |

|            |        | g I                                             | 61              |

|            |        | Configuration parameters for WRITE_1 generation |                 |

|            |        |                                                 | 02<br>63        |

|            | / 1    | 3 4 11 11 2 11 1 11 11 11 11 11 11 11 11 11     |                 |

| A.6. | Configuration parameters for READ_0 generation                  | 63 |

|------|-----------------------------------------------------------------|----|

| A.7. | Configuration parameters for common WRITE_2 generation          | 64 |

| A.8. | Configuration parameters for I/P & O/P buffer generation        | 65 |

| A.9. | Steps to configure the Data-flow manager and make it compatible |    |

|      | to HiTech Global development board                              | 65 |

# List of Abbreviations

Abbreviation Full form

ALU Arithmetic and Logic Unit

AMBA Advanced Microcontroller Bus Architecture

ARM Acorn RISC Machine

ASIC Application Specific Integrated Circuit

AXI Advanced Extensible Interface

C-Link Camera Link

CPU Central Processing Unit

DDR3 Double Data Rate 3

DFC Data-flow Controller

DFM Data-flow Manager

DRAM Dynamic RAM

DSP Digital Signal Processor

FIFO First In First Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

IC Integrated Circuit

I<sup>2</sup>C Inter-integrated Circuit

IP Intellectual Property

ISE Integrated Synthesis Environment

ISim ISE **Sim**ulator LUT Lookup **T**able

MIG Memory Interface Generator

MMU Memory Management Unit

OS Operating System

RAM Random Access Memory

RISC Reduced Instruction Set Computer

RPU Reconfigurable Processing Unit

SDRAM Synchronous **DRAM**

SRAM Static RAM

TDMA Time Division Multiple Aaccess

TIFF Tagged Image File Format

UART Universal Asynchronous Receiver

Transmitter

USB Universal Serial Bus

| VHDL  | VHSIC Hardware Description Language                       |

|-------|-----------------------------------------------------------|

| VHSIC | Very High Speed Integrated Circuit                        |

| WRR   | $\mathbf{W}$ eighted $\mathbf{R}$ ound- $\mathbf{R}$ obin |

# **List of Figures**

| 2.1.  | Mapping virtual address to the physical address using a page table.               | 5  |

|-------|-----------------------------------------------------------------------------------|----|

| 2.2.  | Allocation and de-allocation of memory pages                                      | 6  |

| 2.3.  | Multiplexed access to one physical memory                                         | 6  |

| 2.4.  | Frame grabber structure                                                           | 8  |

| 2.5.  | Architecture of memory controller                                                 | 9  |

| 2.6.  | Two systems memory arbiter block diagram                                          | 11 |

| 2.7.  | Memory hierarchy                                                                  | 13 |

| 3.1.  | Single-channel data-flow manager                                                  | 16 |

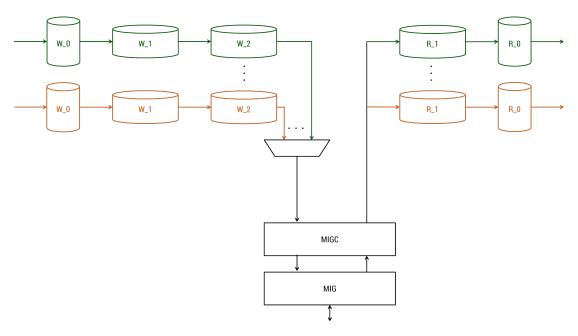

| 3.2.  | Architecture for super-scalar multi-channel data-flow manager                     | 18 |

| 3.3.  | Architecture for super-scalar multi-channel data-flow manager with                |    |

|       | individual WRITE_2                                                                | 19 |

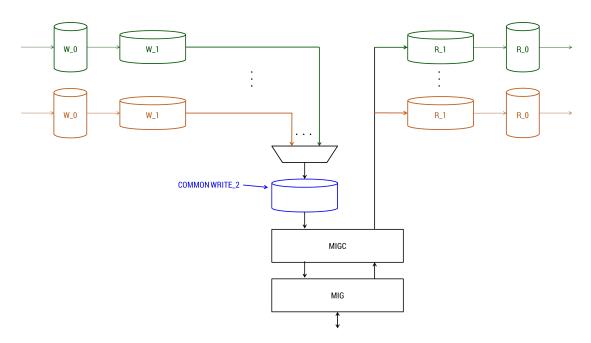

| 3.4.  | Architecture for super-scalar multi-channel data-flow manager with common WRITE_2 | 20 |

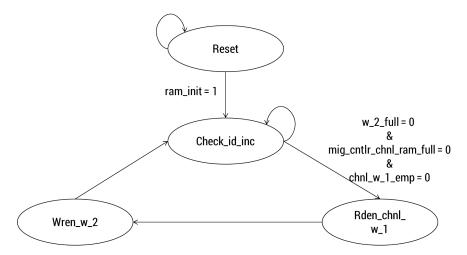

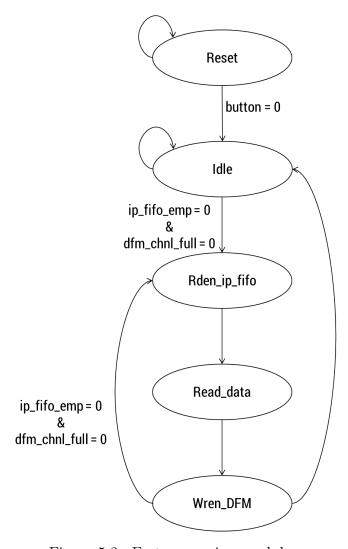

| 3.5.  | Finite state machine for data-flow controller master                              | 22 |

| 3.6.  | Finite state machine for data-flow controller slave                               | 23 |

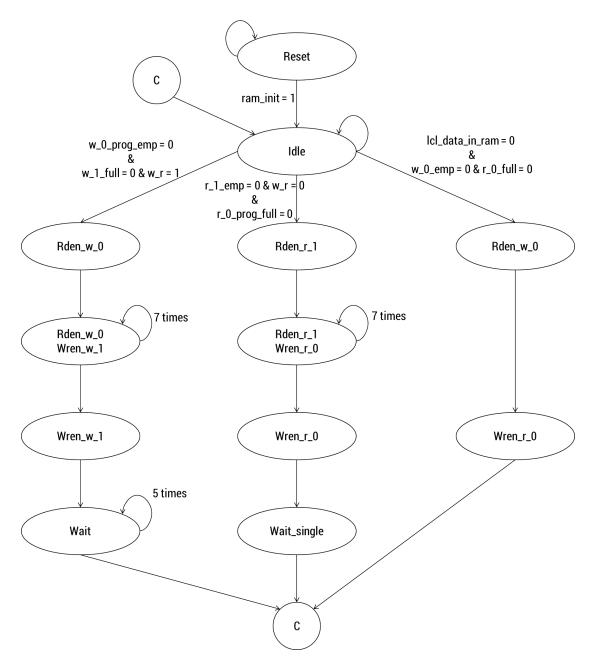

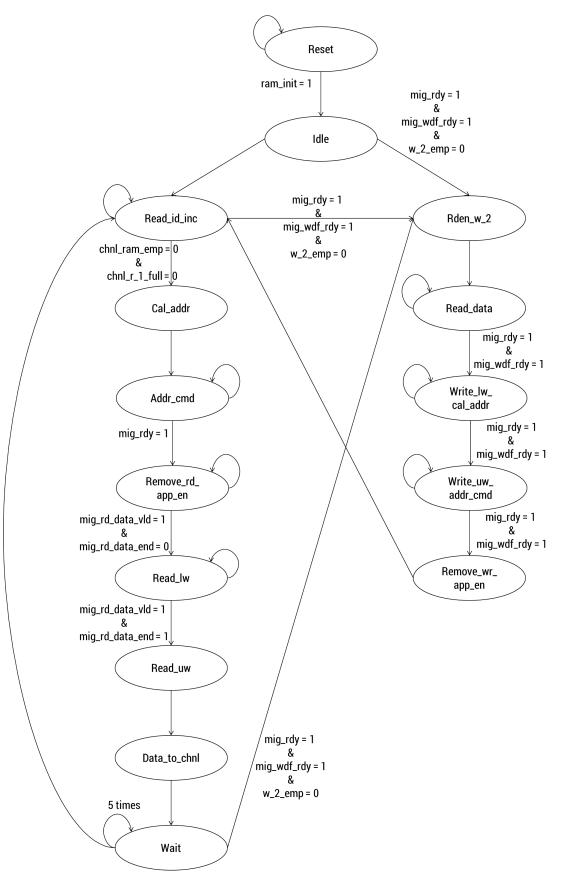

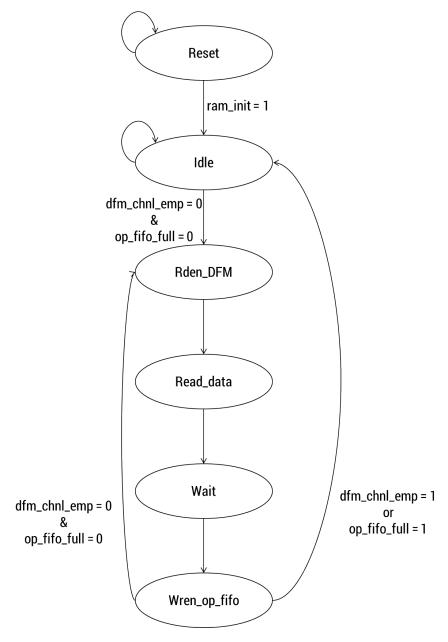

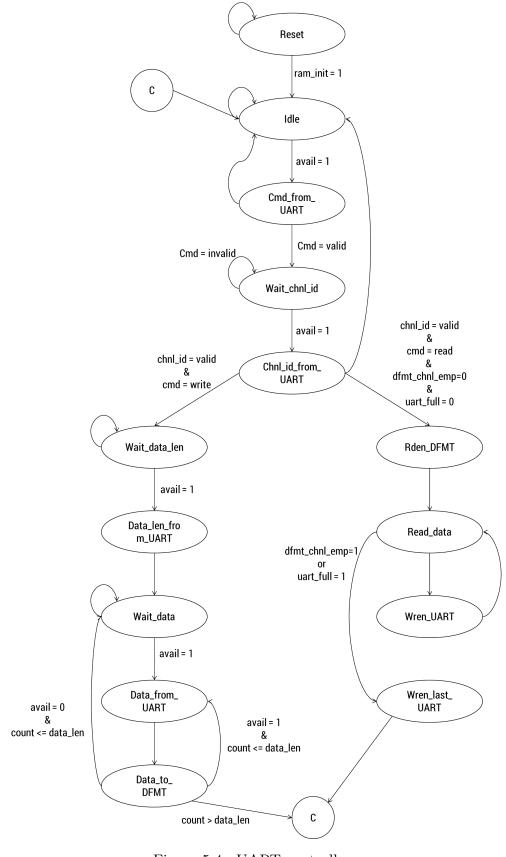

| 3.7.  | Finite state machine for memory interface generator controller $\ . \ . \ .$      | 25 |

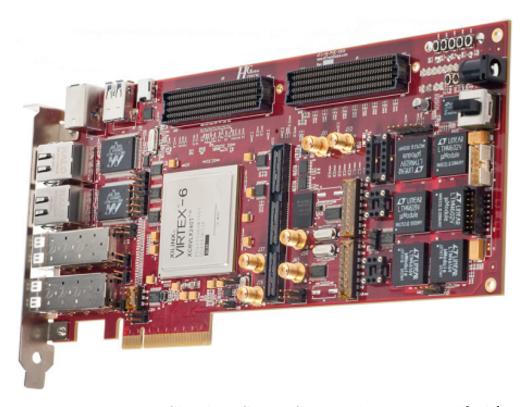

| 4.1.  | HiTech Global HTG-V6-PCIE Development Board                                       | 30 |

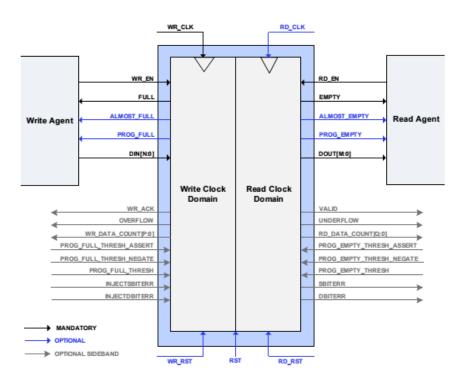

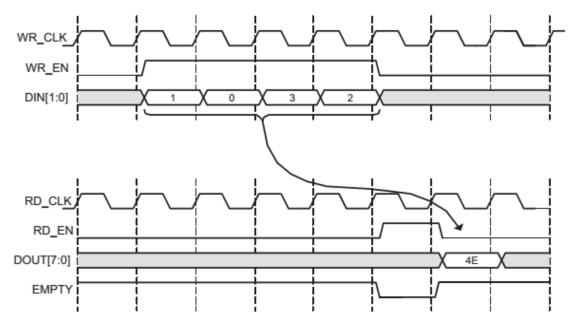

| 4.2.  | Native interface FIFO signal diagram                                              | 33 |

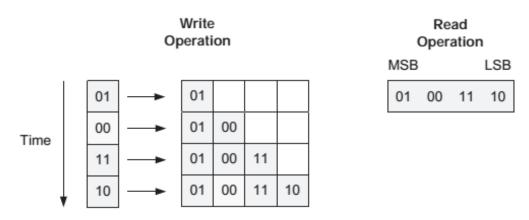

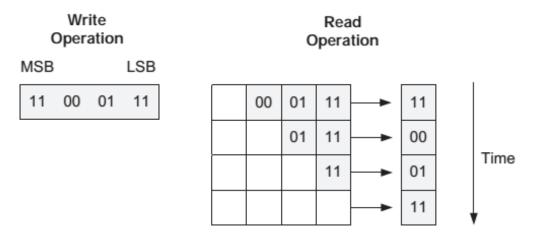

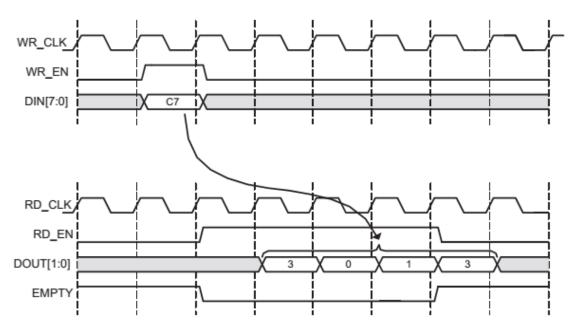

| 4.3.  | 1:4 Aspect ratio FIFO data ordering                                               | 34 |

| 4.4.  | 1:4 Aspect ratio FIFO status flag behaviour                                       | 35 |

| 4.5.  | 4:1 Aspect ratio FIFO data ordering                                               | 35 |

| 4.6.  | 4:1 Aspect ratio FIFO status flag behaviour                                       | 36 |

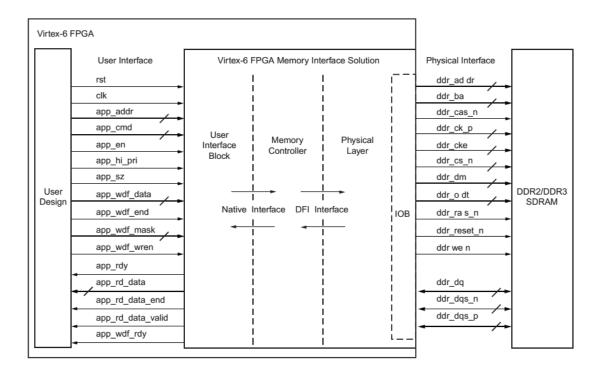

| 4.7.  | User interface Virtex-6 FPGA memory interface solution                            | 39 |

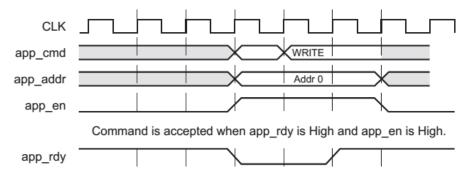

| 4.8.  | Memory interface generator command timing diagram                                 | 40 |

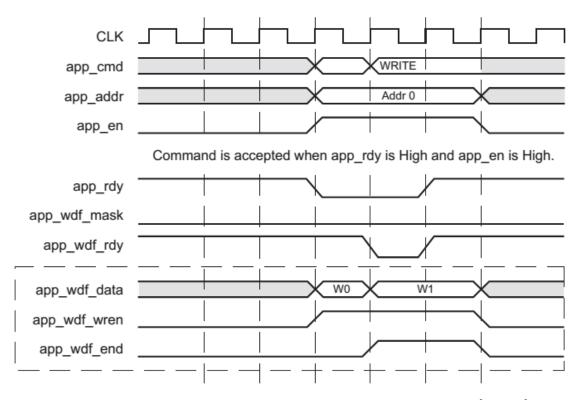

| 4.9.  | Memory interface generator write timing diagram                                   | 40 |

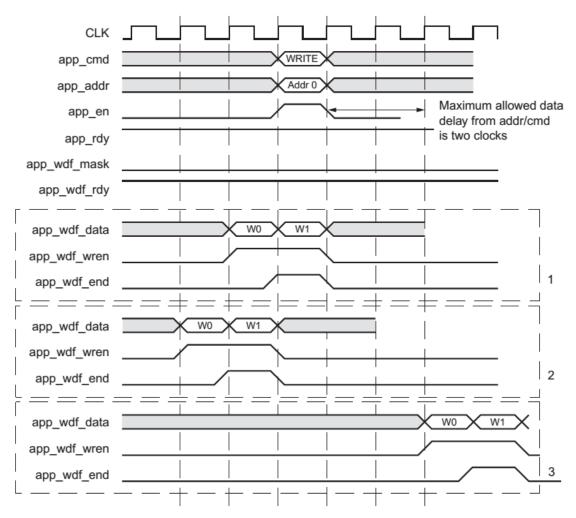

| 4.10. | Memory interface generator write data with respect to command time events         | 41 |

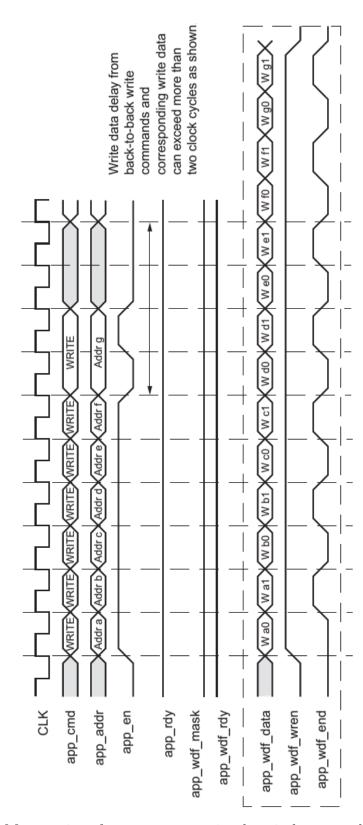

| 4.11. | Memory interface generator write data in burst mode BL8                           | 42 |

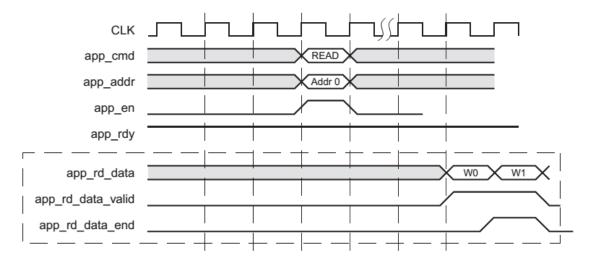

|       | Memory interface generator read timing diagram                                    | 43 |

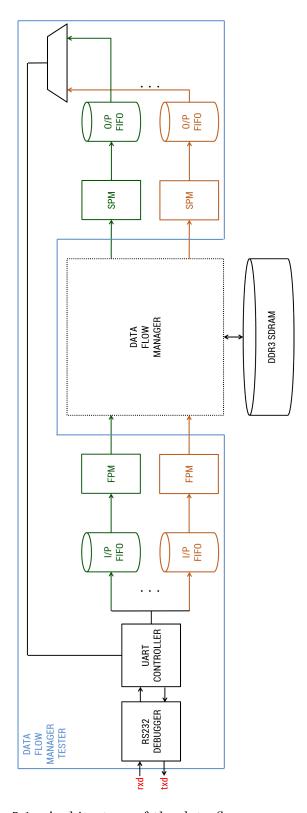

| 5.1.  | Architecture of the data-flow manager tester                                      | 46 |

| 5.2.  | Fast processing module                                                            | 48 |

| 5.3.  | Slow processing module                                                            | 49 |

| 5.4.  | UART controller                                                                   | 51 |

# **List of Tables**

| 3.1. | Port width and memory location width of buffers                    | 15 |

|------|--------------------------------------------------------------------|----|

| 3.2. | Virtual address range for the multiple channels                    | 27 |

| 4.1. | Interface signals of FIFO with independent clock                   | 34 |

| 4.2. | Write flags update latency due to a write operation                | 36 |

| 4.3. | Read flags update latency due to a read operation                  | 36 |

| 4.4. | Write flags update latency due to a read operation                 | 37 |

| 4.5. | Read flags update latency due to a write operation                 | 37 |

| 4.6. | Memory interface generator user interface signals                  | 39 |

| 5.1. | Resource utilization of data-flow manager on Virtex-6 XC6VLX240T   | 52 |

| 5.2. | Timing characteristics of data-flow manager on Virtex-6 XC6VLX240T | 53 |

# 1. Introduction

#### 1.1. Motivation

FPGAs are user-programmable integrated circuits which are extensively being used along with the traditional microprocessors in various fields of applications. FPGAs contain an array of logic blocks, lookup tables (LUT), etc. which are used to implement complex functional blocks. It can be used to implement a hardware functional block with a single purpose (like ASIC) and also have the added feature of re-programmability (like Microprocessor). FPGA combines the main advantages of both ASIC and Microprocessor.

The main advantage of a FPGA based system is its ability to perform the task at a high speed and efficiency. Hardware parallelism is the reason that a FPGA is able to achieve faster speeds and better efficiency thereby achieving higher throughput.

The advantages that FPGAs have over other types of data processing units are:

- 1. They are efficient at parallel data processing. This is a major advantage of FPGA over other reconfigurable ICs like Microprocessors which process data sequentially.

- 2. They are capable of processing large size of data at high speeds. Unlike Microprocessors, those are limited to data processing equivalent to its arithmetic and logic unit (ALU) size (e.g. 8bit, 16bit, 32bit, 64bit).

- 3. They are reliable. Since, FPGAs are configured using hardware description language (HDL), a developer has a complete control, up to the gate level which helps in designing time critical and reliable systems.

- 4. They have a variety of interface options like UART, I<sup>2</sup>C, USB, Ethernet, etc. due to which FPGAs can be interfaced with different kinds of electronic devices.

- 5. They have a broad range of applications. FPGAs are being used in wide areas like Aerospace and Defence, Medical Electronics, Scientific Instruments, Consumer Electronics, Security Systems, Image Processing, Automotive sector, etc.

FPGAs also include some kind of data storage in the form of memory blocks which are used to temporarily buffer the data being processed and push the data from one functional block to another as and when required.

When FPGAs are used for high volume data processing (e.g. the data parallelization mentioned in the research article [SB12]), the amount of data required to be buffered is in the order of few MBs. The amount of memory available on the FPGA is around 2.5MB (combination of the block RAM and distributed RAM on Virtex-6 XC6VLX240T [Vir15]).

This shows that the amount of memory resources available on-board is very less as compared to the data required to be stored in the memory. This is one of the major disadvantages when using FPGA for high volume data processing.

Also, in real world applications when multiple functional entities are combined together to make a bigger entity and work together, the entire system might not yield the expected speed and throughput. One of the problems that the system designers face is where the systems combined together have a difference in the data processing speeds at an individual level.

For example, if there are two entities which are working together to achieve a particular task and the first entity has twice as higher speed of data processing as the second entity. In such a case, the first entity has to wait for the second entity to complete its processing before it can move onto the processing of the next available data input.

Asynchronous buffers (First In First Out - FIFO) are used to handle such problems. Asynchronous FIFOs reduce the amount of the stalling time and thereby reducing the latency of the overall system [Tal14]. But, the amount of FIFOs that can be implemented on an FPGA is also limited by the amount of on-board memory available. These problems further increase when there are multiple instances of such logic blocks which require high amount of data storage.

Within the scope of this master thesis a method has been proposed to increase the on-board memory with the help of external DDR3 SDRAM with an effort to reduce the overall latency of the system and a smooth functioning of all the logic blocks connected to one another.

## 1.2. Structure of the master thesis report

Chapter 2: Provides information about the state of the art which consists of different methods proposed by other researchers to solve the problem similar to the one mentioned above. It describes the idea of creating an arbiter so as to facilitate the flow of data from 2 separate entities to an external RAM. One of the methods presents a concept of a new SDRAM controller designed from scratch without the use of any already available memory controllers provided by Xilinx. Data caching techniques found in the modern processors are also considered to be an idea for the development the solution for this master thesis.

Chapter 3: Describes the concept involved behind the development of base solution for the memory management module i.e. Data Flow Manager (DFM). It also contains different approaches designed in order to improve the DFM and the reason behind selection of a particular approach and its implementation. The architecture of the DFM and all the modules required to develop the final entity are also described and explained in this chapter.

**Chapter 4:** Gives an overview of the hardware and tool chain used to realize the whole system. It explains in brief all the pre-built logic blocks (Intellectual Property Core - IPCore) used in order to implement the DFM.

Chapter 5: Involves the test environment created to evaluate and validate the system function. The architecture of the environment and the structure of all the modules used to create this environment are explained in brief. This chapter also includes the different test scenarios used to verify the working of the system and different results observed and discusses these results in detail.

Chapter 6: Concludes the master thesis, points out the shortcomings of the design. Recommendations for the removal of these shortcoming and bugs are explained and ideas for the future improvements of this topic are proposed.

# 2. State of the Art

# 2.1. Memory management to support multitasking on FPGA-based systems

Klaus Danne of University of Paderborn "introduced a concept of Memory Management Unit (MMU). MMU is designed in a way that is is capable to handle the concurrent operations of multiple tasks to banks of a single external RAM" in research article [Dan04a]. MMU is used to store the state of the currently ongoing task to be able to handle the interrupt from a new task.

The development of a MMU is required to provide abstraction and resource management for the tasks, which are normally provided by the Operating System (OS). In normal case of a computer microprocessor and the OS, the memory management is done with the help of support from the OS and dedicated MMU of the processor. However, in case of the FPGA, MMU is not a dedicated unit but a module created on the FPGA itself to handle the memory management.

The features required for the MMU are [Dan04a]:

- 1. virtual addressing

- 2. management of the external dedicated RAM

- 3. memory caching not needed

- 4. resolution of the task conflicts when multiple tasks require to access the same memory bank

- 5. access to the multiple memory banks in parallel

- 6. tasks are supposed to handle the memory access delays

#### 2.1.1. Virtual addressing

The virtual addressing is required to make the memory addressing independent of the other tasks that are running. Therefore, every task gets a memory slice address starting from 0x00...0 and ends at a value depending upon the size of the memory slice. If all the information regarding the tasks is available beforehand

then the virtual address can be converted to the physical address. This virtual addressing is required, as the number of tasks is not known at the design time.

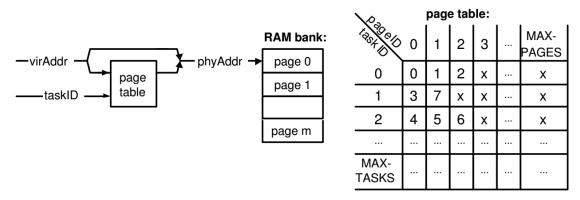

Figure 2.1.: Mapping virtual address to the physical address using a page table [Dan04a]

To implement the address translation at runtime, information regarding the address mapping is needed to be stored in the MMU. Figure 2.1 show an example of the address mapping technique. Here, the page table information is stored in the MMU. The high-word of the virtual address along with the task ID is used to address the page table and the output of the page table is used as the high-word of the physical address. The low-word of the virtual address is used directly as the low-word of the physical address. The width of the higher part of the word and the lower part of the work depend completely on the value of the chosen page size. Due to such an easy virtual address mapping technique the page size is limited to be a power of two.

There are two additional features of using such a simple method [Dan04a]:

- 1. **Memory protection:** Due to presence of the page table, the MMU is aware if a particular task is trying to access a memory location outside its address bounds. This helps in avoiding errors created due to faulty tasks.

- 2. **Inter task communication:** Inter task communication is possible via access to the same physical memory locations. This can be done by setting the page table entry to same value for two different tasks. Additional handshake signal mechanisms have to be implemented to avoid both the tasks trying to read the same memory location at the same time.

## 2.1.2. Dynamic memory allocation

Dynamic memory management is required when new tasks enter a system. MMU allows a task to allocate or de-allocate memory dynamically at runtime with the

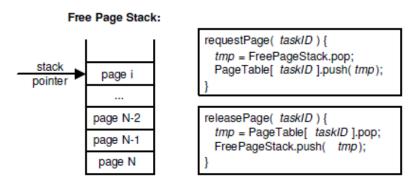

help of 'requestPage(taskID)' function and 'releasePage(taskID)' function. Figure 2.2 shows the function snippet along with the free page stack, which stores the information regarding the allocated or de-allocated pages.

Figure 2.2.: Allocation and de-allocation of memory pages [Dan04a]

#### 2.1.3. Priority based scheduled memory access

As discussed previously, inter task communication is possible via the access to the same physical memory location. For this to happen, the address and data bus of the memory have to be multiplexed. Figure 2.3 show the physical architecture of this mechanism.

Figure 2.3.: Multiplexed access to one physical memory [Dan04a]

A control signal is used to manipulate the access given to memory for a particular task. If a single task requests access then the MMU switches the multiplexers so that the task is able to complete its write/read operation. If multiple tasks require access to the memory at the same time, a priority based scheduling of the memory access is done to guarantee error free operation that is well within its timing constraints.

# 2.2. Memory management abstraction for self-reconfigurable video processing

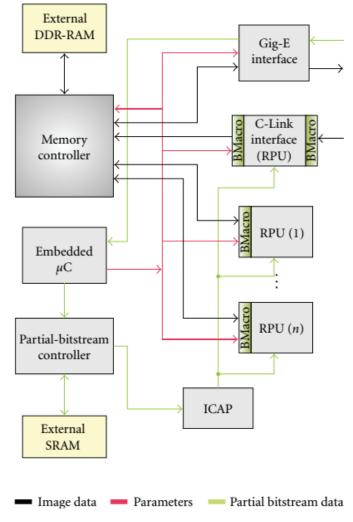

Kurt Franz Ackermann of Darmstadt University of Technology "presents a concept for an SDRAM controller targeting video processing platforms with dynamically reconfigurable processing units (RPUs)" in research article [AHIG09]. Multiple modules present on the FPGA for the task of video processing require the data to be stored and read from the external DDR3 SDRAM.

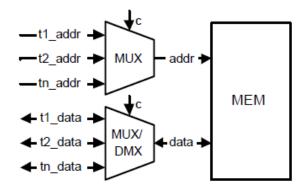

Figure 2.4 represents the Frame grabber structure and the data flow required for the reconfigurable video processing platform. The Camera-Link (C-Link) acts as an interface between the frame grabber and the camera. The frame received from the C-Link is first written to the external RAM via the memory controller. Here, the memory controller acts as the main communication centre for all the different modules. There are n different RPUs which work on the video frames buffered in the memory. There is Gigabit Ethernet interface which connects the whole system to the computer. When all the RPUs complete processing the data, the result is then transferred to the computer via the Ethernet. This whole cycle then repeats for the next video frame.

The memory controller developed for the task requires being complex so that it is capable to provide data to all the random data requests generated by the complex video processing algorithms. Also, the complexity of the controller increases as the RAM clients are unaware of the data organization in the memory.

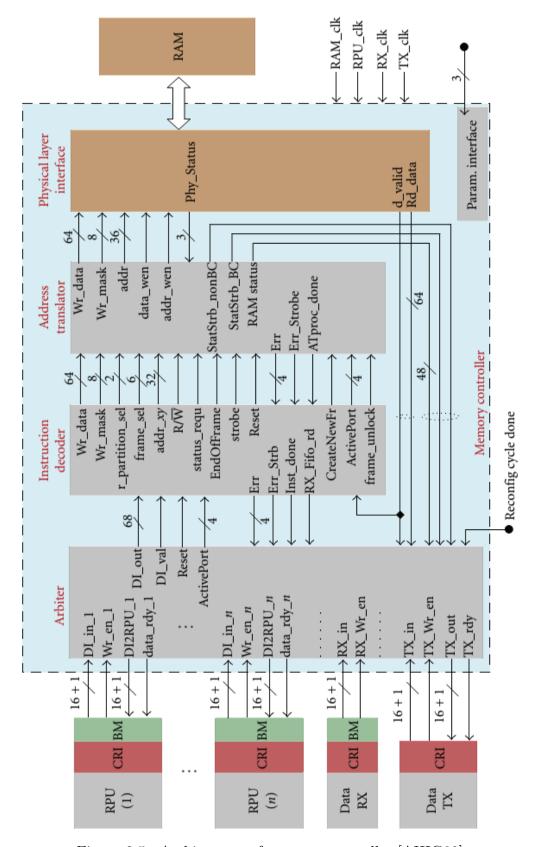

The proposed memory controller architecture is presented in the figure 2.5. The functionality provided by the memory controller is [AHIG09]:

- 1. Support for multiple RAM clients

- 2. Priority arbitration

- 3. Support for read/write data bursts

- 4. Memory partitioning

- 5. Frame-based ring-buffers

- 6. Support for variable frame dimensions

- 7. Support for high-level addressing

- 8. Providing high-level status information

Figure 2.4.: Frame grabber structure [AHIG09]

#### 2.2.1. Arbiter

The main advantage of the FPGA based system is ability of its different modules to work in parallel with respect to each other. In such a case, there is possibility of these different modules (RPUs) request data from the RAM at the same time. An arbiter needs to be implemented which can take care of the requests and satisfy the quality of the system.

The arbiter works on a weighted round-robin (WRR) algorithm which provides the RPUs with the chance to complete its data operation depending upon the clients' priorities.

Figure 2.5.: Architecture of memory controller [AHIG09]

#### 2.2.2. Instruction decoder

The Instruction decoder works on the commands received from the different clients. It decodes the instructions like "create-new-frame, unlock, end-of-frame" [AHIG09] and does the required pre-processing for the instructions. The decoder acts as a bridge between the arbiter and the address translator. Its allow the valid instructions for the address translation while invalid instructions generate appropriate error codes which are sent back to the arbiter.

#### 2.2.3. Address translator

The Address translator handles the job of the maintaining the data in the physical RAM in suitable memory structures. It provides the required abstraction of the memory to the clients. The data addressed by the clients is in the units of pixels, lines and frames. Address translator partitions the data to avoid data corruption. The partitions are organized as frame ring-buffers which give access to the latest frames given by the clients.

## 2.3. FPGA design for DDR3 memory

Laura Fischer and Yura Pyatnychko of Worcester Polytechnic Institute "presents a memory arbiter system capable of sanctioning two systems to interact with a single DDR3 SDRAM memory" in their bachelor thesis [FP12]. The DDR3 memory controller developed by Xilinx supports communication between one system and memory. In real word FPGA-based applications, there are chances of more than one systems trying to communicate with the memory. If two such systems try to communicate with the memory simultaneously, there is a possibility of data corruption in case of data writing and false data reception in case of reading. Hence, a traffic controller which keeps check on such multiple simultaneous requests and provides the response in a manner such that it avoids the data corruption is required. The arbiter not only avoids the requests collision but also maintains their order to ensure the data available in the memory is up-to-date. The requirements for such memory arbiter are listed as follows [FP12]:

- 1. Arbiter should take into consideration the memory's refresh rate

- 2. Arbiter must maintain the requests from the two systems in order

- 3. Arbiter must keep a check on the amount of time a system uses the memory

Figure 2.6.: Two systems memory arbiter block diagram [FP12]

The figure 2.6 contains the design of two systems connected to the memory via an Arbiter block. The arbiter contains all the necessary FIFOs required to buffer the read and write commands and the write data before they are transferred to the memory controller. There are two address FIFOs to store the addresses of the read and write commands. There is a 64-to-512 FIFO which is used to store the data to be written to the memory. A 512-to-64 FIFO is also available to store the data read back from the memory. The arbiter uses two signals: "other\_sys\_switch" and "this\_sys\_switch" which check the current system that is using the memory controller and limits the other one from using it. There are two copies of arbiter running simultaneously with in accordance to each other. The inter communication of these two arbiter blocks allows the two systems to maintain an error free data communication with the common external memory module.

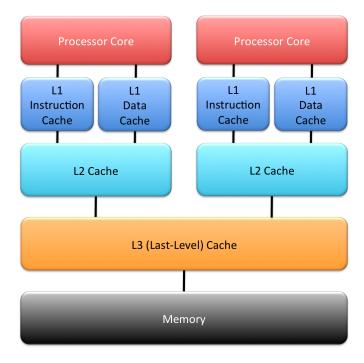

## 2.4. Caching techniques in x86 processors

The Central Processing Unit (CPU) of a computer runs at a higher clock speed as compared to that of a memory module. The speed at which the data is provided to the CPU from the RAM creates a bottleneck in the operation. To avoid such bottlenecks and to hide the memory access latencies from the CPU the concept of data caching came into existence.

Caching consists of storing the most frequently used data in a memory as near to the CPU as possible. This cache memory is much faster as compared to the RAM. Along with being faster, this cache is also expensive and hence available in smaller quantities in comparison to that of a RAM. At the system reset, the cache is completely empty. At the first request, the data is read from the main memory and passed on to the CPU. A copy of this data is also maintained in the cache for further use. The initial read from the main memory costs high latency but it cannot be avoided. But all subsequent accesses to the same data are met with minimum latency possible as the data is already present in the cache memory.

Since the amount of cache is very small and is not capable of incorporating lot of data, a new level of cache is introduced which is slower than the previous cache but bigger in size as compared to the previous cache. The cache nearer to the CPU is called level 1 (L1) cache and the cache between L1 and the RAM is called level 2 (L2) cache.

L1 and L2 caches are available on the CPU chip itself and that is the reason why their size is very limited. To overcome the size limitations, the motherboards on which the CPU is connected also contain a level 3 (L3) cache. This leads to a memory hierarchy.

Figure 2.7.: Memory hierarchy [Hei15]

Figure 2.7 show the memory hierarchy found in the modern day computer. The size of the cache memories for the Intel's Sky Lake Micro-architecture is as follows [Ark]:

- 1. L1 Cache (Instruction) 64KB per core

- 2. L1 Cache (Data) 64KB per core

- 3. L2 Cache 256KB per core

- 4. L3 Cache 8192KB shared

# 2.5. Feature requirements for the on-board memory extension

In the previous sections of this chapter, different ideas regarding the implementation of the memory controller to increase the amount of memory available on-board with the help of external RAM have been discussed. There are different advantages and disadvantages of these methods with respect to the solution required for the problem mentioned in the chapter 1. Based on the ideas and concepts used above, the features required or the concepts that can possibly be useful for the development of the memory extension are:

- 1. Virtual addressing: So that the different clients are not dependent on one another for the addressing.

- 2. Memory partitioning: To divide the memory equally between different clients.

- 3. Data caching: To satisfy data requests immediately whenever possible.

- 4. Scheduling algorithm: To ensure that every client gets a chance for data operation without collision with respect to another.

- 5. Memory protection: To ensure data written to a particular memory partition belongs to the same client.

- 6. Strict data ordering: To maintain data order when data appears in a long continuous stream.

- 7. Scalable architecture: To incorporate the variable number of clients.

# 3. Concept, Design and Implementation

As discussed in the previous chapter, an entity which reflects the working similar to that of the caching technique in case of computer processors needs to be implemented for the FPGA. Along with the low latency data-flow it also needs to be capable of implementing data-flow not only from one input entity to one output entity but it needs to be capable of managing the data-flow from multiple input entities to corresponding output entities.

Data-flow manager (DFM) is the solution to our problems which has the facility to transfer data from multiple input sources to the corresponding destinations directly if destination is ready to accept the data or via the external RAM as and when required.

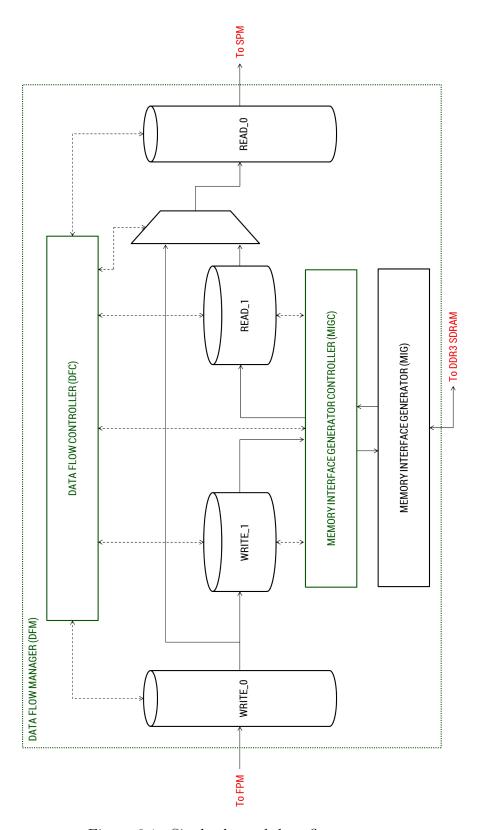

# 3.1. Single-channel data-flow manager

The figure 3.1 portrays the architecture of a single channel DFM. WRITE\_0 and READ\_0 denote the level 0 buffers and WRITE\_1 and READ\_1 denote the level 1 buffers. The input and output data widths of each buffer are as mentioned in the table 3.1.

| Buffer  |              |              | Memory location |

|---------|--------------|--------------|-----------------|

| Buildi  | width (bits) | width (bits) | size (bits)     |

| WRITE_0 | 8            | 64           | 64              |

| READ_0  | 64           | 8            | 64              |

| WRITE_1 | 64           | 512          | 512             |

| READ_1  | 512          | 64           | 512             |

Table 3.1.: Port width and memory location width of buffers

Figure 3.1.: Single-channel data-flow manager

Here the data-flow occurs via two different paths:

- 1. From WRITE\_0 to READ\_0 directly.

- 2. From WRITE\_0 to READ\_0 via WRITE\_1,DDR3 SDRAM and READ\_1.

The data is directly transferred from WRITE\_0 to READ\_0 if there is free memory location in the READ\_0 buffer and there is no data present in any other buffers or external RAM. When the buffer READ\_0 runs full then the data from WRITE\_0 is transferred to WRITE\_1 and it follows the second data path mentioned above.

The decision regarding the path that the data will flow through is being taken by Data Flow Controller (DFC). DFC keeps track of the empty and full signals of all the buffers and also on signals from the Memory Interface Generator Controller (MIGC) which helps in deciding if there is empty memory location in READ\_0 and absence of data at any other buffer level or in RAM so as to allow a direct data transfer from WRITE\_0 to READ\_0 or not.

DFC not only makes the decision but also provides all the necessary signals to all the others entities which are required to initiate the data transfer.

The job of the MIGC is to read data from the WRITE\_1 and generate appropriate write address required to write the data to RAM and provides this information along with write command and enable signals to the Memory Interface Generator (MIG). It also checks if there is empty memory location in READ\_1 and generates appropriate read address. It provides the read address, read command and enable signal to MIG so as to initiate a read from the RAM. The data read from the RAM is then written to READ\_1.

MIG is an Intellectual Property Core (IPCore) provided by Xilinx which helps in easy data write/read to/from external DDR3 SDRAM. Chapter 4 contains detailed information regarding the working of the MIG.

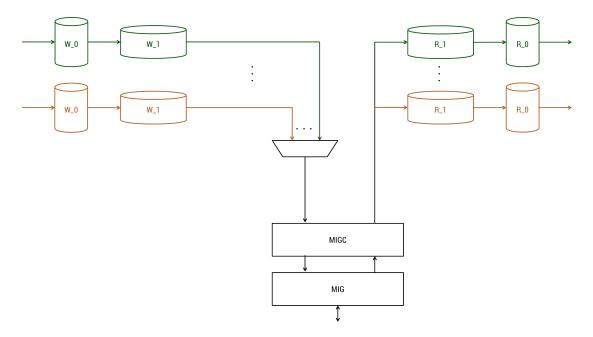

# 3.2. Multi-channel data-flow manager

Working of multi-channel DFM is such that local data transfers occur in each and every channel in parallel with respect to one another. Whenever the READ\_0 of any channel gets full, there arises a need for the data to be stored in RAM. This data is first transferred to the next level WRITE\_1 buffer. Now there are multiple WRITE\_1 buffers which expect to write the data to RAM. A basic round robin manner is used where each and every channel gets a chance to write data to the RAM. Similarly, reading from RAM also happens in a round robin manner. There are few variations to a multi-channel DFM which are mentioned below which help

us in achieving the desired goal of low latency data-flow along with limited amount of on-board resource usage.

#### 3.2.1. Super-scalar approach

Figure 3.2 depicts the very basic and logical version to implement a multi-channel DFM from a single-channel DFM. Here, the multiple channels are created by the replication of the modules present in the single channel without any extra data buffers.

The advantage to this design is that it is very easy to implement with minor modifications to the data-flow controlling modules.

Due to round robin manner, each and every channel gets less number of chances for data transfer to RAM. Hence, the possibility of the buffers on the write side running full increases. This is a major disadvantage to this approach and this problem keeps increasing in direct proportion to the increase in the number of channels.

Figure 3.2.: Architecture for super-scalar multi-channel data-flow manager

## 3.2.2. Super-scalar approach with individual WRITE\_2

Figure 3.3 represents the next approach towards the development of multi-channel DFM. To reduce the risk of write buffers running full an extra level of write buffer

has been introduced. WRITE\_2 buffer has both input and output data width of 512bits.Addition of extra level of buffer increases the amount of data that can be stored on the write side thereby reducing the pressure of data transfer to the RAM.

This approach overcomes the problem mentioned in the previous approach but it gives rise to another problem. It increases the amount of on-board memory usage which is already limited.

Figure 3.3.: Architecture for super-scalar multi-channel data-flow manager with individual WRITE  $_{2}$

## 3.2.3. Super-scalar approach with common WRITE\_2

Figure 3.4 describes the final approach which is a trade-off between the previous two approaches. The input data to all the channels comes from different sources and is incoming at different rate. Therefore, the channels where the input is connected to a source with low data rate might not have a risk of write buffers running full. Hence, instead of connecting WRITE\_2 buffer to all the channels, there is only need to attach these level 2 buffers to only required channels. But for this to be possible there has to be prior information about the data rate of all the sources.

In absence of the data rate information a generalized WRITE\_2 buffer has to be implemented. Hence, a common WRITE\_2 buffer is used which is shared by all the channels and its memory locations will be in majority occupied by the channels

with a high data rate input.

This approach not only reduces the risk of buffers running full but also keeps a control over the amount of on-board resources used. Hence, this approach has been chosen to develop the multi-channel DFM. Also, the multi-channel DFM is designed in a generic way such that the user can choose the number of channels from a range of 1 to 32.

Figure 3.4.: Architecture for super-scalar multi-channel data-flow manager with common WRITE\_2

## 3.3. Common WRITE\_2 FIFO

The common write buffer has both input port and output port width of 517bits. The lower 512bits of the buffer location is filled with the data received from the WRITE\_1 buffer of the channel. The higher 5bits are used to store the id of the channel from where the data is received from. The Xilinx FIFO IPCore is used to create all the buffers. The core generator does not directly provide an option to modify the data width of the ports. Hence, the number of bits for the channel id is limited to 5bits which limits the maximum number of channels possible to 32.

#### 3.4. Data-flow controller

As discussed in the section 3.1, DFC is the main component which handles the job of decision making for the data path selection. In case of a single-channel DFM a single DFC is present which communicates with all the other components. But when the numbers of channels increase, as in case of the multi-channel DFM, there comes into existence multiple DFCs which need to communicate with a single MIGC.

To make it easier for data synchronization between multiple channels and to avoid increasing the complexity of the DFC to incorporate the status of other channels, DFC is split into two parts: DFC Master and DFC Slave.

DFC Slave now plays the same role as the DFC in the case of single-channel DFM except for handling the data transfer between WRITE\_1 to WRITE\_2 and between MIGC and READ\_1.

DFC Master handles the round robin iteration of all the channels and data transfer from the WRITE\_1 to WRITE\_2 as and when required. On the other hand, MIGC iterates through the READ\_1 and provides the data to the read buffer as the need arises.

#### 3.4.1. Data-flow controller master

Data Flow Controller Master is designed as per the state machine in the figure 3.5. The main job of DFC Master is to transfer data from the WRITE\_1 of each channel to common WRITE\_2 in a round robin manner.

The DFC Master checks the empty signal (CHNL\_W\_1\_EMP) of WRITE\_1 buffer of the current channel, full signal (W\_2\_FULL) of WRITE\_2 and full signal coming from MIGC (MIG\_CNTLR\_CHNL\_RAM\_FULL) for the memory slice dedicated for the current channel and decides whether to initiate the data transfer or not. Then it increments the channel id and repeats the same for the next channel. DFC Master gives the appropriate read enable signal, write enable signal and select line for the multiplexer and confirms the data transfer.

The data width of the output from WRITE\_1 is 512bits and the data width of the input to WRITE\_2 is 517bits. The 5bits of current channel id not only acts as the select line for the mux but also serve as the higher 5bits of the data input to the WRITE\_2. The channel id stored along with the data in the WRITE\_2 is used by MIGC to calculate the appropriate memory location address for the write operation.

Figure 3.5.: Finite state machine for data-flow controller master

#### 3.4.2. Data-flow controller slave

Data Flow Controller Slave is designed as per the state machine in the figure 3.6. The main job of DFC Slave is to handle the local data transfer. The local data transfer comprises of 3 data transfer operations which are:

#### 1. Data flow from WRITE\_0 to READ\_0

Initially, after the system reset, there is no data available in any of the buffers. In this case, there is no need for data to be stored to the RAM as there is enough space in the READ\_0 buffer. Hence, direct transfer of data from WRITE\_0 to READ\_0 occurs.

Since, the memory location size of both the buffers is same only one free location in READ\_0 is required to initiate the data transfer. Hence, the full signal (R\_0\_FULL) of READ\_0 and empty signal (W\_0\_EMP) of WRITE\_0 are used to make the decision.

LCL\_DATA\_IN\_RAM is a signal driven by empty signals of the current channel WRITE\_1, current channel READ\_1, common WRITE\_2 and data available in RAM signal (GBL\_DATA\_IN\_RAM) of the current channel memory slice from MIGC. LCL\_DATA\_IN\_RAM signal assures that no data is present at any other location.

#### 2. Data flow from WRITE\_0 to WRITE\_1

Only after READ\_0 runs full, there arises a need to transfer the data to RAM. To achieve this, at first, data should be transferred from WRITE\_0

Figure 3.6.: Finite state machine for data-flow controller slave

#### to WRITE\_1.

Memory location size of WRITE\_0 is 64bits while that of WRITE\_1 is 512bits. Data stored in 8 memory locations from WRITE\_0 needs to be transferred to WRITE\_1. Hence, instead of empty signal (W\_0\_EMP), programmable empty signal (W\_0\_PROG\_EMP) is used which assures there are at least 8 memory locations filled in WRITE\_0.

W\_R is a signal which stores the information about the next operation to be performed and keep alternating between write and read. The operation between WRITE\_0 and READ\_0 has the highest priority and the other two operations are given equal priority so as to confirm that the data written to the WRITE\_0 reaches RAM via WRITE\_1 and data read from RAM to READ\_1 is read by READ\_0.

The extra wait states are required to give time to the FIFOs to update its full, programmable full, empty and programmable empty signals. Detailed information regarding the FIFOs is mentioned in chapter 4.

#### 3. Data flow from READ\_1 to READ\_0

In this operation, memory location size of READ\_1 is 512bits and that of READ\_0 is 64 bits. Hence, data once read from READ\_1 has to occupy 8 memory locations in READ\_0. Hence, the programmable full signal (R\_0\_PROG\_FULL) of READ\_0 is used instead of full signal (R\_0\_FULL).

## 3.5. Memory interface generator controller

Memory Interface Generator Controller (MIGC) is designed using the finite state machine mentioned in figure 3.7. The objective of MIGC is to handle the read and write requests to the Memory Interface Generator (MIG).

RAM\_INIT denotes the PHY\_INIT\_DONE signal coming from the MIG. This is the most important signal which is being used by all the finite state machines. RAM\_INIT indicated that the external RAM has been successfully calibrated. Hence, no operation should be carried out until the RAM\_INIT signal is asserted.

MIG\_RDY is the second most important signal after the signal RAM\_INIT. The process of writing to the RAM or reading from the RAM should not move forward unless the MIG is ready to handle requests. Write and read operations are given equal priority. At the end of any one of the operation, the chance is given for the other operation to execute. The conditions for the state transitioning are defined in such a way that the above mentioned rule is followed.

Write operation starts if there is any data present in the common WRITE\_2 buffer and MIG is ready to process the data and that the write bus of the MIG is also available. These conditions are verified by the empty signal (W\_2\_EMP) of WRITE\_2, MIG\_RDY and MIG\_WDF\_RDY. The 512bit data is read from the WRITE\_2.

Figure 3.7.: Finite state machine for memory interface generator controller

During this time, the address for the write memory location is also calculated and given along with the write command. MIG\_ADDR and MIG\_CMD denote the address bus and the command bus while MIG\_EN is the signal which is given to indicate the MIG that valid address, command and data is present on the input ports.

For read operation, a round robin manner is implemented. MIGC checks the full signal (CHNL\_R\_1\_FULL) of READ\_1 of each channel one after the other and decides if there is free memory location for a data to be read from the RAM and written to the READ\_1 buffer of the current channel. Depending upon the channel id the read address is calculated and given along with the read command and enable signal. During write operation 512bits data is split into two words of 256bits and then written. Similar to the write operation, data read from the RAM is also available in two words of 256bits each. The data is indicated by a valid signal (MIG\_RD\_DATA\_VALID) while the last word is indicated by the read end signal (MIG\_RD\_DATA\_END).

The address calculation for both write and read operation is based on the write pointer, read pointer and data count. These 3 values are maintained and stored for each and every channel in an array of composite data type. Also depending on these values and operations, full signal (CHNL\_RAM\_FULL) and empty signal (CHNL\_RAM\_EMP) are available which are used by other modules as a deciding factor for their operations.

There are two generics defined for the MIGC and a constant value used for setting different vector sizes. They are as follows:

- 1. NO\_OF\_CHANNELS: This generic helps to indicate the entity about the total number of channels generated. The channel id starts from 0 to NO\_OF\_CHANNELS-1. For example, in case NO\_OF\_CHANNELS is set to 4, the channels have id from 0 to 3. The minimum value that NO\_OF\_CHANNELS can have is 1 while the maximum value is 32.

- 2. **DATA\_DEPTH:** DATA\_DEPTH indicates the number of memory locations of the external memory module reserved for a particular channel. The value set here should be a power of 2. The depth set here is used for all the channels irrespective of their need. The user should ensure that the product of DATA\_DEPTH, NO\_OF\_CHANNELS and memory location width should be less than or equal to the maximum size of the RAM.

- 3. **VECTOR\_WIDTH:** It is a constant that is calculated from the value of the DATA\_DEPTH. VECTOR\_WIDTH indicates the number of bits required to address all the memory locations for the set DATA\_DEPTH. For example, if the DATA\_DEPTH is set to 8 memory locations then the VECTOR\_WIDTH calculated is 3bits.

The composite data type used for the storage of the address pointers and the data count is as shown below.

```

type channel_info is

record

chnl_write_ptr : std_logic_vector (VECTOR_WIDTH-1 downto 0);

chnl_read_ptr : std_logic_vector (VECTOR_WIDTH-1 downto 0);

chnl_data_count : std_logic_vector (VECTOR_WIDTH-1 downto 0);

end record;

```