Yu Zhang

Performance Improvement of Hypervisors for HPC Workload

Yu Zhang

# Performance Improvement of Hypervisors for HPC Workload

TECHNISCHE UNIVERSITÄT CHEMNITZ

Universitätsverlag Chemnitz 2018

#### Impressum

### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Angaben sind im Internet über http://www.dnb.de abrufbar.

Das Werk - ausgenommen Zitate, Cover, Logo TU Chemnitz und Bildmaterial im Text steht unter der Creative-Commons-Lizenz Namensnennung 4.0 International (CC BY 4.0) http://creativecommons.org/licences/by/4.0/deed.de

Titelgrafik: Yu Zhang Satz/Layout: Yu Zhang

Technische Universität Chemnitz/Universitätsbibliothek Universitätsverlag Chemnitz 09107 Chemnitz https://www.tu-chemnitz.de/ub/univerlag

readbox unipress in der readbox publishing GmbH Am Hawerkamp 31 48155 Münster http://unipress.readbox.net

ISBN 978-3-96100-069-2

http://nbn-resolving.de/urn:nbn:de:bsz:ch1-qucosa2-318258

# TECHNISCHE UNIVERSITÄT CHEMNITZ

# Performance Improvement of Hypervisors for HPC Workload

Dissertation zur Erlangung des akademischen Grades

Dr.-Ing

Herr M. Eng Yu Zhang geboren am 7.Juli 1980 in Huhhot, China

Fakultät für Informatik an der Technischen Universität Chemnitz

Dekan : Gutachter : Prof. Dr.-rer. nat. Wolfram Hardt Prof. Dr.-Ing. habil. Matthias Werner Prof. Dr.-Ing. Alejandro Masrur

Tag der Einreichung :30.01.2018Tag der Verteidigung :03.07.2018

**Zhang, Yu** Performance Improvement of Hypervisors for HPC Workload Dissertation, Fakultät für Informatik Technical University of Chemnitz, Januar 2019

## Acknowledgments

With eight years efforts, the PhD. study is slowly drawing to an end. Many people have rendered their help, expressed concern, and encouraged me. All these had strengthened my confidence to overcome the difficulties all along the way and go so far to create this work.

First, I sincerely thank my former supervisor, Prof. Wolfgang Rehm, who had offered me the opportunity to pursue the PhD study in TU Chemnitz, arranged the equipments and environment that are necessary for scientific research. More importantly, under the guidance of Prof. Rehm, I was ushered to the domains of Computer Architecture, HPC and System Virtualization. Efforts on a topic of these aspects lead to this dissertation.

Second, I would like to express my heartful gratitude to my current supervisor, Prof. Matthias Werner, who has sincerely rendered his academic supervision on my research topic and arranged a very comfortable environment for me to complete this research task. Without Prof. Werner's generous support, I cannot image to complete this research. As an earnest scholar and upright man, Prof. Werner really impressed me.

My thanks extend to my colleagues in the two professors research groups. René Oertel, Nico Mittenzwey, Hendrik Nöll and Johannes Hiltscher had rendered me invaluable suggestions on many issues, from equipment, publication to professional technical skills to my stay in Chemnitz.

With his patience and experience, Dr. Peter Tröger helped me to avoid quite a lot of incorrect ideas for research and drafting each chapter of this dissertation. I benefited enormously from his comments, feedback, and the conversation with him.

It is always my best memory to attend the conferences of EMS 2013 in Manchester, BigData-Science'14 in Beijing, Euro-Par VHPC'15 in Vienna, and ISC VHPC'17 in Frankfurt. I really feel gratitude for many unknown reviewers who evaluate my contributions positively to give me the chances to contact with world's excellent researchers and scholars. During these conferences, the chairs, Prof. David Al-Dabass, Dr. Alvin Chin, and Dr. Michael Alexander, had very nice talks with me. Dr. Andrew J. Younge, whom I get to know at ISC VHPC'17, gave me valuable constructive comments for a portion of this manuscript.

Prof. Andreas Goerdt encourages me to keep on even at the tough moments. Other friends, Wang Jian, Chou Chih-Ying, and Bai Qiong supported me all through the past eight years. They are true friends with whom I can share joy and frustration.

Furthermore, I would like to mention the China Scholarship Council (CSC), whose financing makes most of this research possible and the Deutscher Akademischer Austauschdienst (DAAD), who also sponsored me in the framework of a research project in the last year.

This manuscript is finally proofread by Ms. Jennifer Hofmann and Ms. Christine Jakobs. They took great patience to scrutinize the lengthy text, correct the grammatical and typographical errors, punctuation, spelling, and inconsistencies. Their efforts had helped me to produce a significantly clearer and more professional scientific work. A few lines of words could never be enough to express my gratitude.

Finally, I express my gratitude to my parents and my brother, who silently supported me all through the years with their love, concern and understanding from thousands of miles away. I dedicate this book to my father, who loved me so much but left me forever before the submission.

## Abstract

The virtualization technology has many excellent features beneficial for today's high-performance computing (HPC). It enables more flexible and effective utilization of the computing resources. However, a major barrier for its wide acceptance in HPC domain lies in the relative large performance loss for workloads. Of the major performance-influencing factors, memory management subsystem for virtual machines is a potential source of performance loss.

Many efforts have been invested in seeking the solutions to reduce the performance overhead in guest memory address translation process. This work contributes two novel solutions - "DPMS" and "STDP". Both of them are presented conceptually and implemented partially for a hypervisor - KVM. The benchmark results for DPMS show that the performance for a number of workloads that are sensitive to paging methods can be more or less improved through the adoption of this solution. STDP illustrates that it is feasible to reduce the performance overhead in the second-dimension paging for those workloads that cannot make good use of the TLB.

# Zusammenfassung

Virtualisierungstechnologie verfügt über viele hervorragende Eigenschaften, die für das heutige Hochleistungsrechnen von Vorteil sind. Es ermöglicht eine flexiblere und effektivere Nutzung der Rechenressourcen. Ein Haupthindernis für Akzeptanz in der HPC-Domäne liegt jedoch in dem relativ großen Leistungsverlust für Workloads. Von den wichtigsten leistungsbeeinflussenden Faktoren ist das Speicherverwaltung-Subsystem für virtuelle Maschinen eine potenzielle Quelle der Leistungsverluste.

Es wurden viele Anstrengungen unternommen, um Lösungen zu finden, die den Leistungsaufwand beim Konvertieren von Gastspeicheradressen reduzieren. Diese Arbeit liefert zwei neue Lösungen "DPMS" und "STDP". Beide werden konzeptionell vorgestellt und teilweise für einen Hypervisor - KVM - implementiert. Die Benchmark-Ergebnisse für DPMS zeigen, dass die Leistung für eine Reihe von pagingverfahren-spezifischen Workloads durch die Einführung dieser Lösung mehr oder weniger verbessert werden kann. STDP veranschaulicht, dass es möglich ist, den Leistungsaufwand im zweidimensionale Paging für diejenigen Workloads zu reduzieren, die die von dem TLB anbietende Vorteile nicht gut ausnutzen können.

# Contents

| Li             | st of                    | Figures                                               | xvii                                                 |

|----------------|--------------------------|-------------------------------------------------------|------------------------------------------------------|

| Li             | st of                    | Tables                                                | xix                                                  |

| Li             | st of                    | Abbreviations                                         | xxi                                                  |

| 1              | Intr                     | oduction                                              | 1                                                    |

|                | 1.1<br>1.2<br>1.3<br>1.4 | Background                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 2 Related Work |                          | ted Work                                              | 13                                                   |

|                | 2.1<br>2.2<br>2.3<br>2.4 | System Virtualization                                 | 17<br>21                                             |

| 3              | A S                      | udy of the Performance Loss for Memory Virtualization | 25                                                   |

|                | 3.1<br>3.2<br>3.3        | HPC Workload Deployment Patterns                      | 27<br>29<br>29<br>29<br>29<br>30                     |

|                    |                | AMD $FX^{tm}$ -8150 (Bulldozer)                                | 30 |  |  |

|--------------------|----------------|----------------------------------------------------------------|----|--|--|

|                    |                | 3.3.3 System Software                                          | 31 |  |  |

|                    | 3.4            | Performance for Memory Paging                                  | 31 |  |  |

|                    | 3.5            | Summary                                                        | 38 |  |  |

|                    |                |                                                                |    |  |  |

| 4                  |                | MS - Dynamic Paging Method Switching and STDP - Simplified Two | 39 |  |  |

| Dimensional Paging |                |                                                                |    |  |  |

|                    | 4.1            | Reflections and Solutions                                      | 40 |  |  |

|                    |                | 4.1.1 Dynamic Paging Method Switching                          | 40 |  |  |

|                    |                | 4.1.2 STDP with Large Page Table                               | 40 |  |  |

|                    | 4.2            | DPMS - Dynamic Paging Method Switching                         | 41 |  |  |

|                    |                | 4.2.1 Performance Data Sampling                                | 41 |  |  |

|                    |                | 4.2.2 Data Processing                                          | 42 |  |  |

|                    |                | 4.2.3 Decision Making                                          | 42 |  |  |

|                    |                | 4.2.4 Switching Mechanism                                      | 43 |  |  |

|                    | 4.3            | STDP - Simplified Two-Dimensional Paging                       | 46 |  |  |

|                    |                | 4.3.1 Revisiting the Current Paging Scheme                     | 46 |  |  |

|                    |                | 4.3.2 Restructured Page Table                                  | 50 |  |  |

|                    |                | 4.3.3 Page Fault Handling in TDP                               | 50 |  |  |

|                    |                | 4.3.4 Adaptive Hardware MMU                                    | 52 |  |  |

|                    | 4.4            | Summary                                                        | 52 |  |  |

| _                  | -              |                                                                |    |  |  |

| 5                  | Imp            | plementation                                                   | 55 |  |  |

|                    | 5.1            | QEMU-KVM Hypervisor Analysis                                   | 55 |  |  |

|                    |                | 5.1.1 About QEMU                                               | 56 |  |  |

|                    |                | Main Components                                                | 59 |  |  |

|                    |                | 5.1.2 About KVM                                                | 60 |  |  |

|                    |                | Guest Creation and Execution                                   | 60 |  |  |

|                    | 5.2            | Parameter Study for DPMS                                       | 62 |  |  |

|                    | 5.3            | DPMS on QEMU-KVM for x86-64                                    | 70 |  |  |

|                    |                | 5.3.1 Performance Data Sampling                                | 70 |  |  |

|                    |                | 5.3.2 Data Processing                                          | 73 |  |  |

|                    |                | 5.3.3 Decision Making                                          | 73 |  |  |

|                    |                | 5.3.4 Switching Mechanism                                      | 74 |  |  |

|                    |                | 5.3.5 Repetitive Mechanism                                     | 79 |  |  |

|                    |                | 5.3.6 PMC Mechanism in QEMU-KVM Context                        | 80 |  |  |

|                    |                | 5.3.7 DPMS for Multi-Core Processor                            | 81 |  |  |

|                    | 5.4            | STDP on QEMU-KVM for x86-64                                    | 82 |  |  |

|                    |                | 5.4.1 Restructured Page Table                                  | 83 |  |  |

|                    |                | 5.4.2 Adaptive MMU for TDP                                     | 85 |  |  |

|                    | 5.5            | Summary                                                        | 87 |  |  |

| 6                  | $\mathbf{Exp}$ | periments and Evaluation                                       | 89 |  |  |

|                    | 6.1            | Objective                                                      | 89 |  |  |

|                    | 6.2            | Testing Design                                                 | 90 |  |  |

|                    | <b>_</b>       | 6.2.1 Functional Correctness Test                              | 91 |  |  |

|                    |                | Performance Data Sampling                                      | 91 |  |  |

|                    |                | Decision Making                                                | 91 |  |  |

|                    |                | Paging Method Switching                                        | 91 |  |  |

|                    |                | 6.2.2 Performance Test                                         | 92 |  |  |

|    | <ul><li>6.3</li><li>6.4</li></ul>                                                                  | Test and Benchmark Results of DPMS                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>93</li> <li>93</li> <li>93</li> <li>93</li> <li>94</li> <li>94</li> <li>95</li> <li>95</li> </ul> |

|----|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 7  | Oth                                                                                                | er Aspects of Performance Loss and Future Work                                                                                                                                                                                                                                                                                                                                           | 97                                                                                                         |

|    | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul>                                                      | Processor and Scheduling Aspect                                                                                                                                                                                                                                                                                                                                                          | $105 \\ 107 \\ 107$                                                                                        |

| 8  | Con                                                                                                | nclusions                                                                                                                                                                                                                                                                                                                                                                                | 111                                                                                                        |

| Bi | ibliog                                                                                             | graphy                                                                                                                                                                                                                                                                                                                                                                                   | 113                                                                                                        |

|    | 0                                                                                                  | , april                                                                                                                                                                                                                                                                                                                                                                                  | 110                                                                                                        |

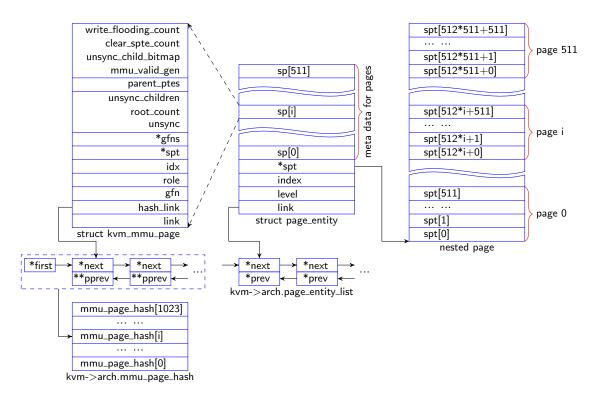

|    |                                                                                                    | ne Data Structures in KVM                                                                                                                                                                                                                                                                                                                                                                | 113                                                                                                        |

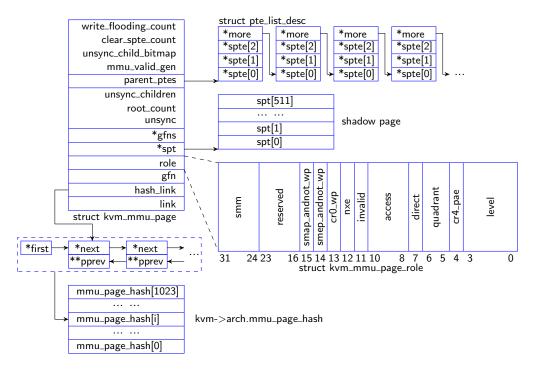

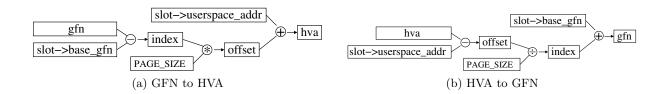

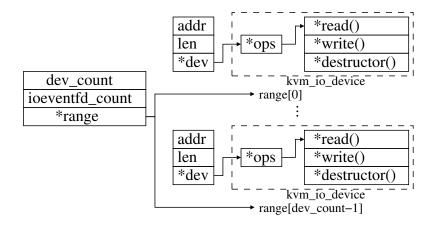

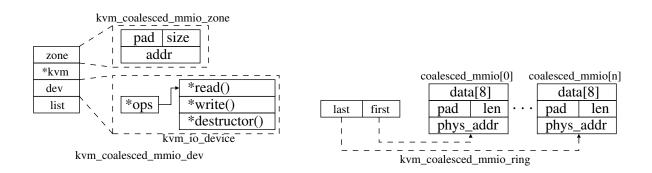

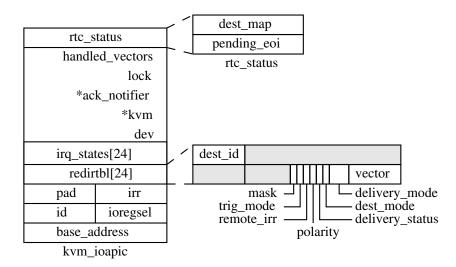

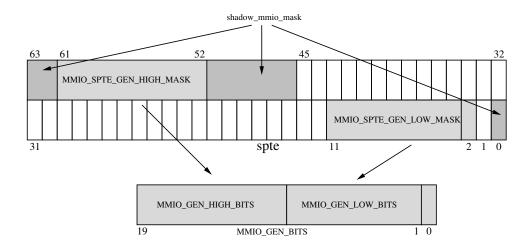

|    | Som<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8<br>A.9<br>A.10<br>A.11<br>A.12         |                                                                                                                                                                                                                                                                                                                                                                                          | <b>123</b><br>123<br>123<br>123<br>124<br>124<br>124<br>124                                                |

|    | Som<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8<br>A.9<br>A.10<br>A.11<br>A.12<br>A.13 | ne Data Structures in KVM         Searching of kvm_mem_slot         Translation between GFN and HVA         kvm_memory_region and kvm_userspace_memory_region         kvm_io_bus         kvm_coalesced_mmio_dev and kvm_coalesced_mmio_ring         kvm_ioapic         interrupt message         kvm_lapic         iterator         kvm_mmuslot         gen_MMIO         2 pte_list_desc | 123<br>123<br>123<br>124<br>124<br>124<br>125<br>125<br>125<br>125<br>126<br>126<br>126                    |

# List of Figures

| $1.1 \\ 1.2$ | Evolution of the processors3Growth of the supercomputer performance4                |

|--------------|-------------------------------------------------------------------------------------|

| 1.3          | Performance, power, scale of supercomputers                                         |

| 1.4          | System virtualization                                                               |

| 1.5          | Problem domain on the road map of virtualization's evolution                        |

| 1.6          | Outline of the thesis                                                               |

| 2.1          | Stack layout of the virtual machine                                                 |

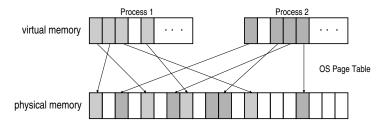

| 2.2          | Memory address translation in physical machines                                     |

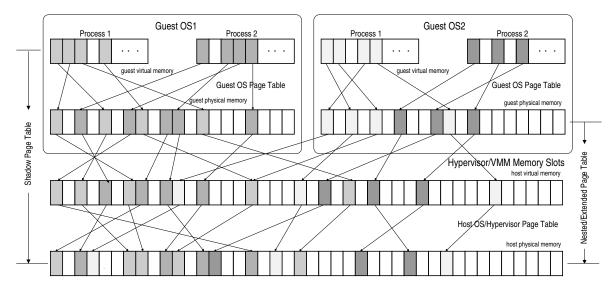

| 2.3          | Memory address translation in virtual machines                                      |

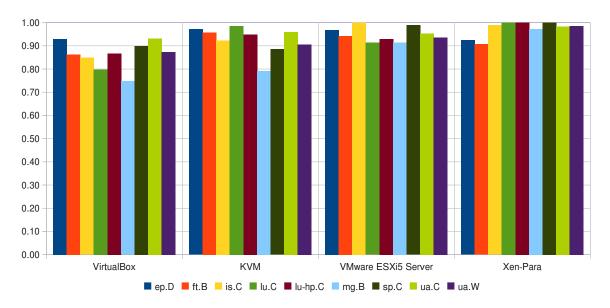

| 2.4          | Normalized performance of NAS in typical virtual environments                       |

| 3.1          | Typical HPC system architecture and the constitution of performance loss $\dots 26$ |

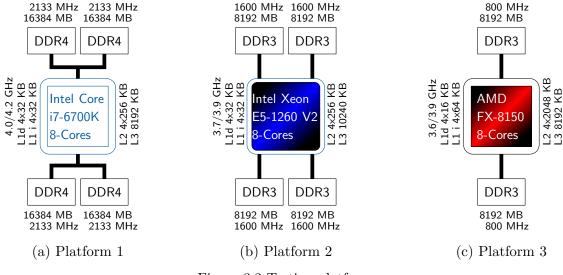

| 3.2          | Testing platforms                                                                   |

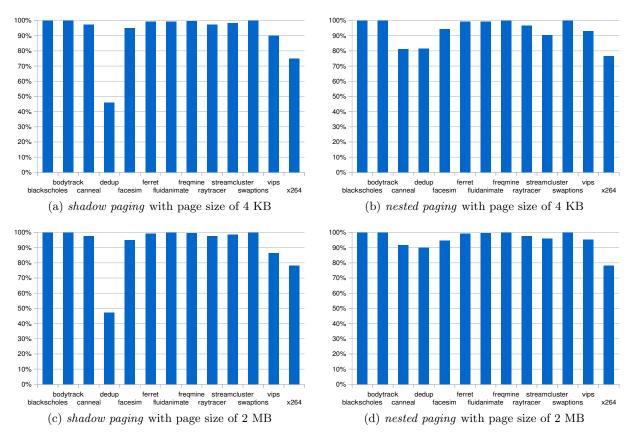

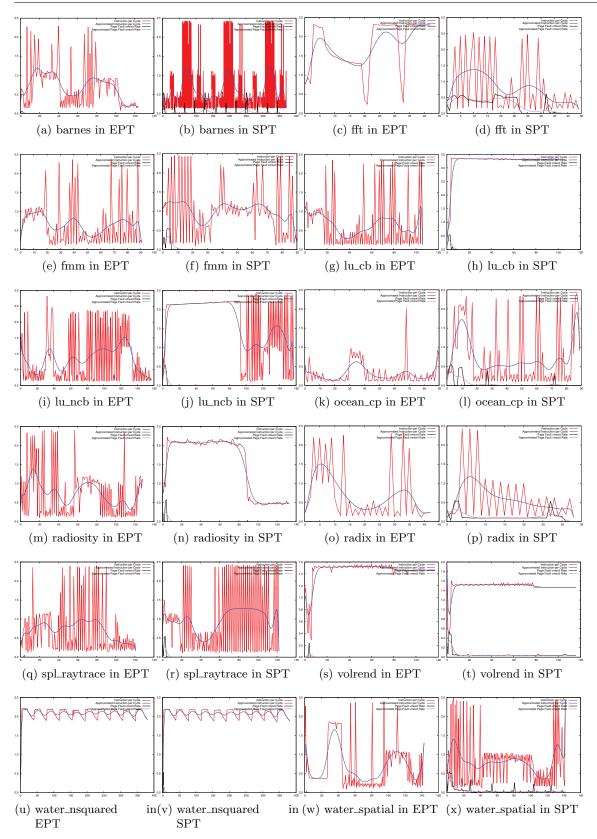

| 3.3          | The normalized performances of <i>shadow paging</i> and <i>nested paging</i>        |

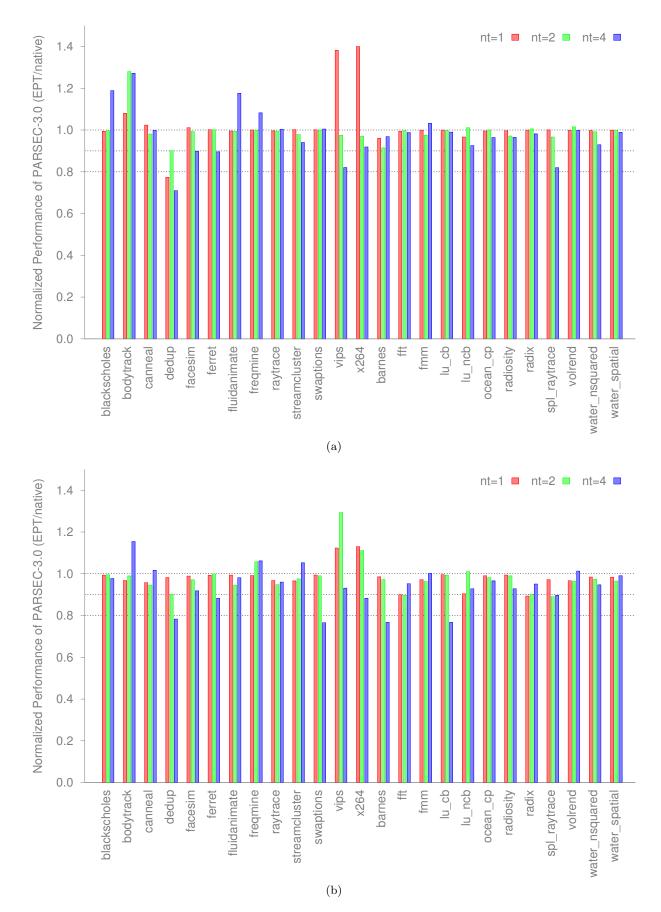

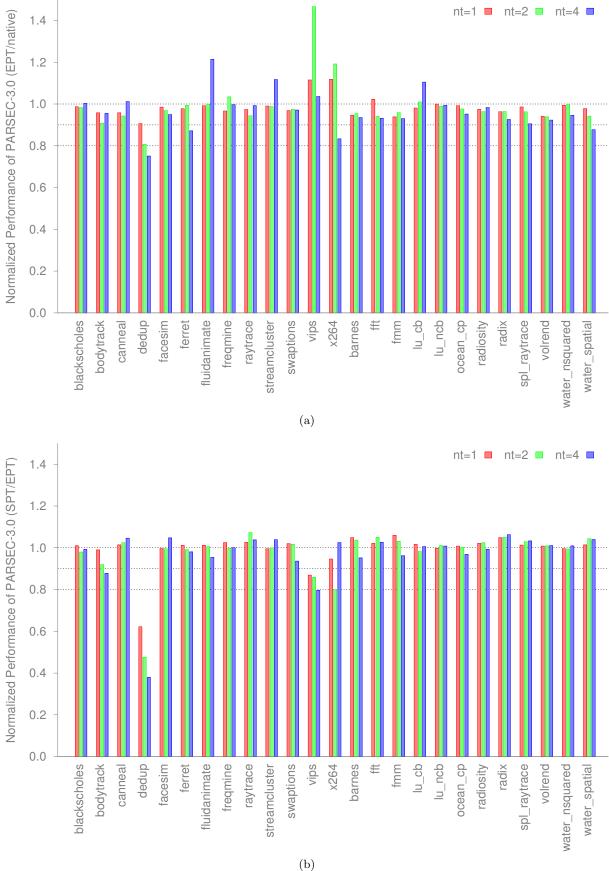

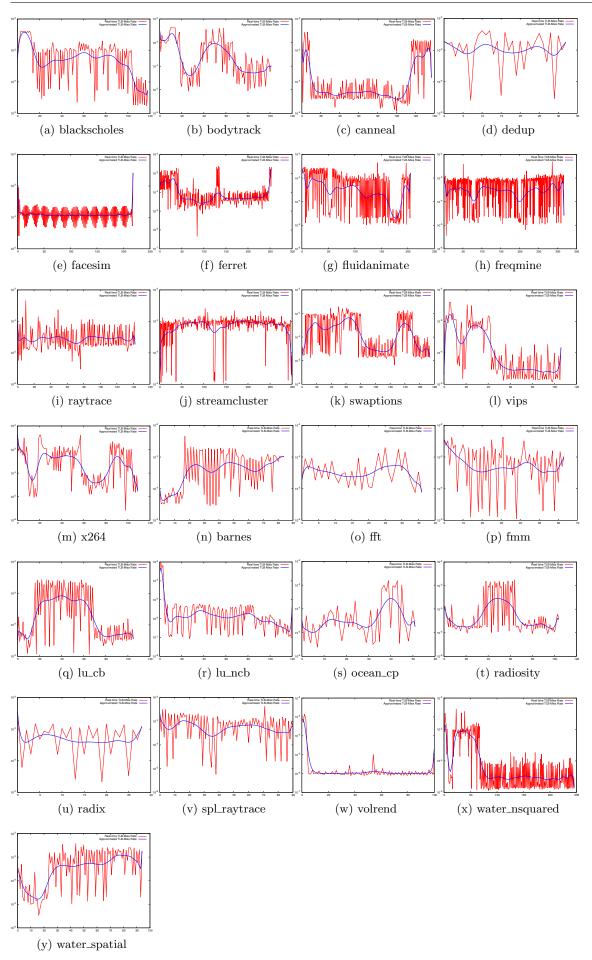

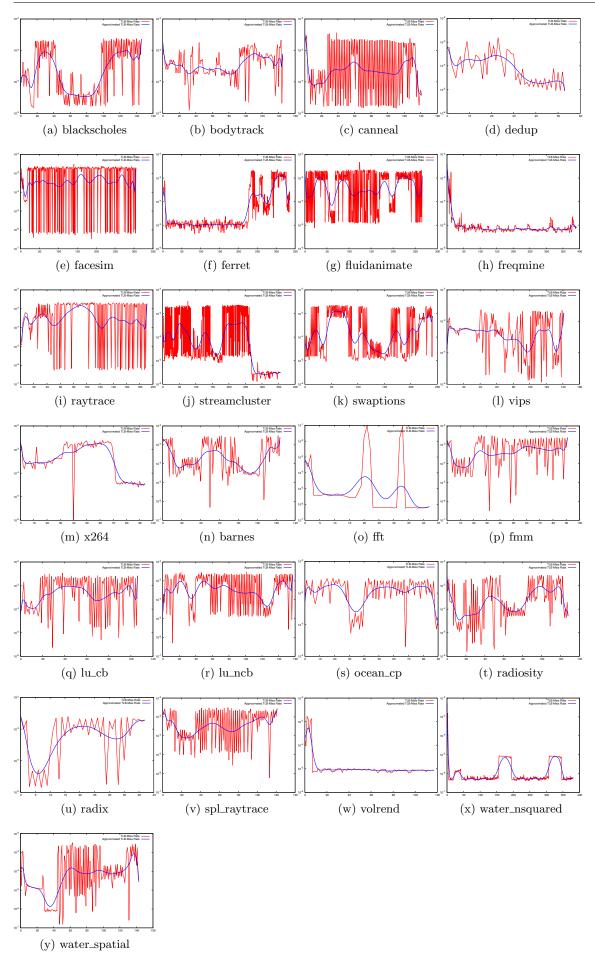

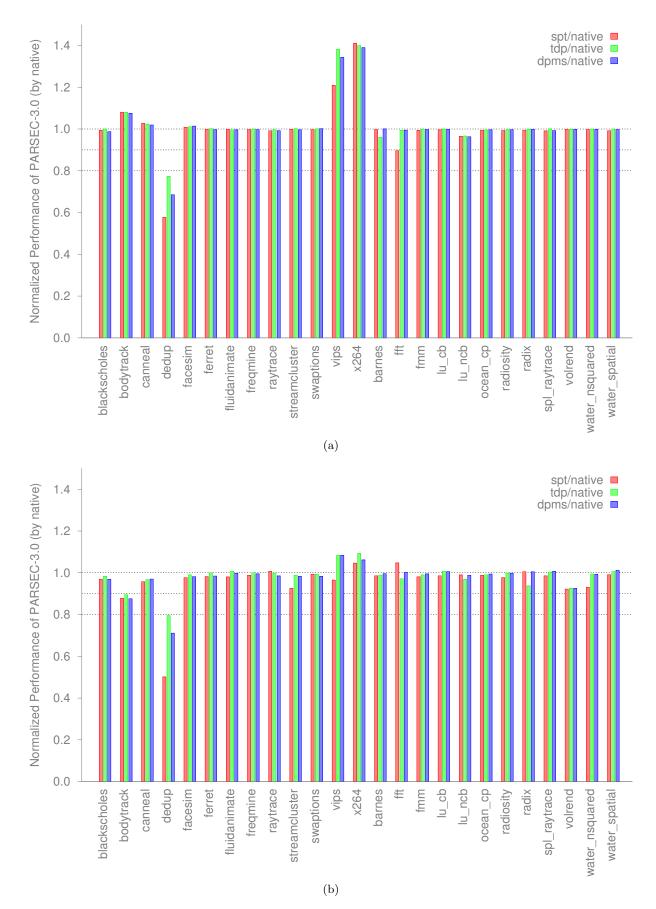

| 3.4          | Normalized performance of PARSEC 3.0 in KVM                                         |

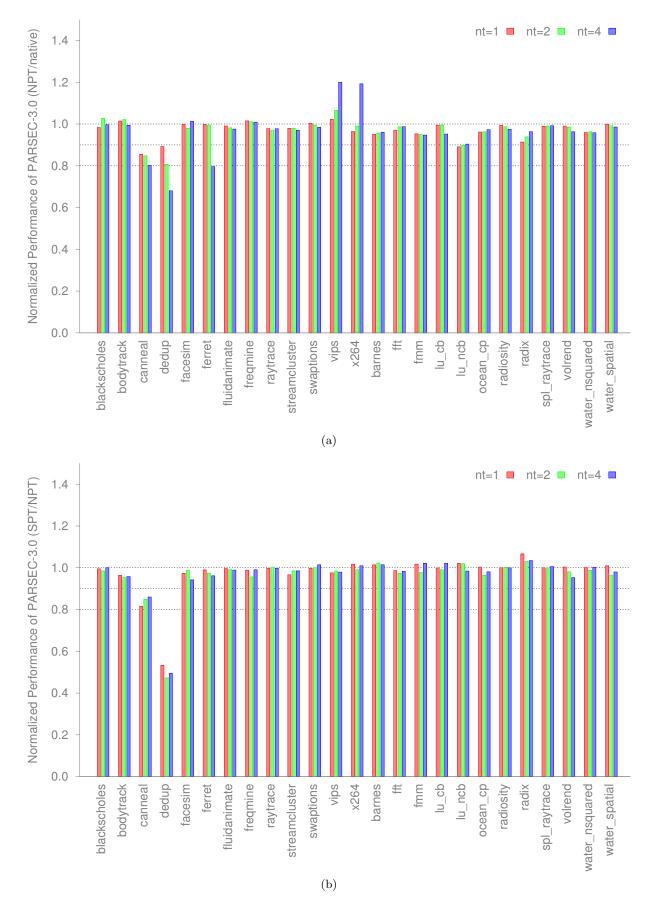

| 3.5          | Normalized performance and comparison on Platform 3                                 |

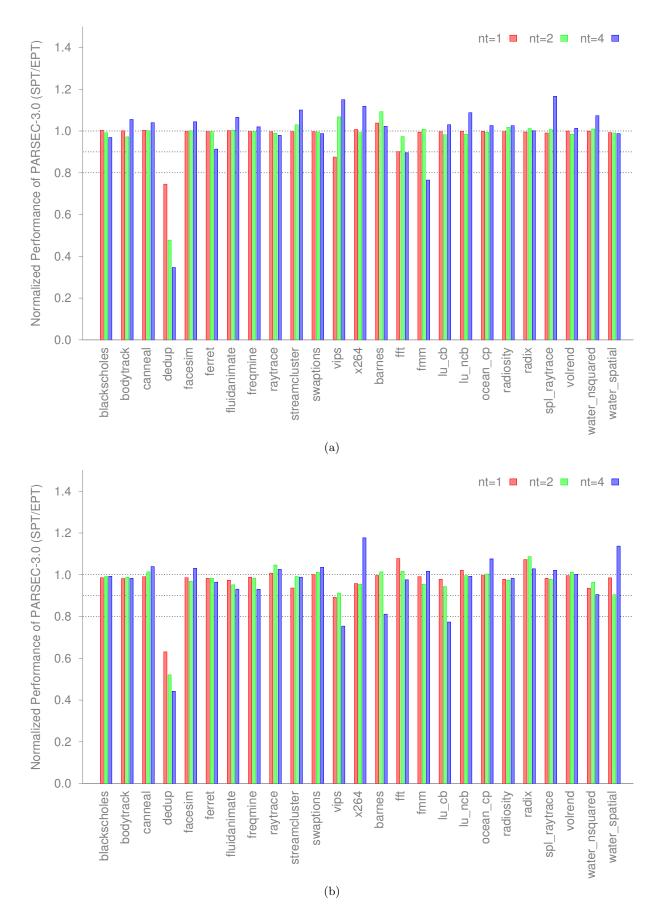

| 3.6          | Performance comparison between SPT and EPT                                          |

| 3.7          | Performance comparison with the page table size of 1 GB                             |

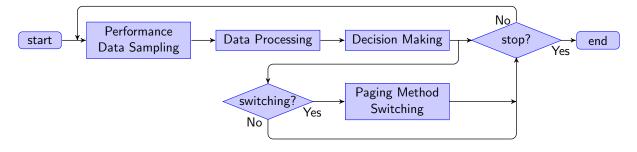

| 4.1          | High-level design of DPMS 41                                                        |

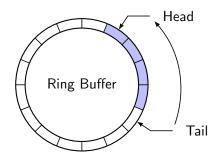

| 4.2          | Ring buffer update                                                                  |

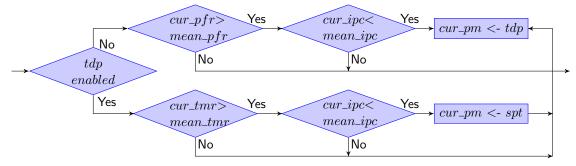

| 4.3          | Flow chart of a basic algorithm for <i>Decision Making</i>                          |

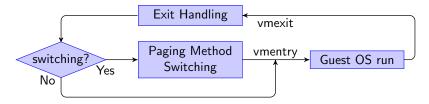

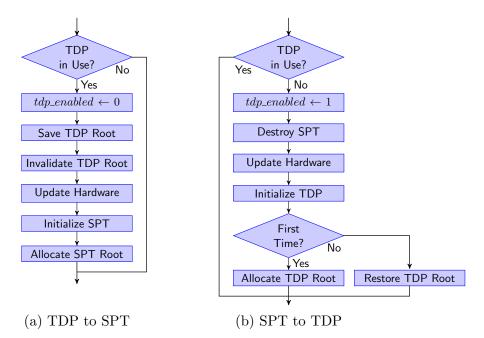

| 4.4          | Occasion for PM switching in the execution flow                                     |

| 4.5          | Basic operations for Paging Method Switching 45                                     |

| 4.6          | High-level Design of STDP 46                                                        |

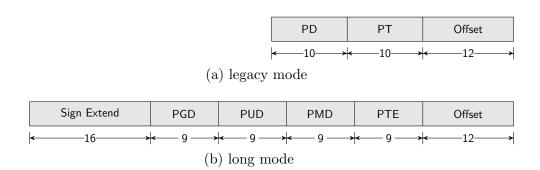

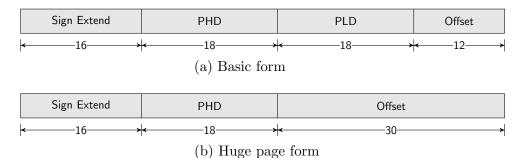

| 4.7          | Breakdown of the logical address for x86-64                                         |

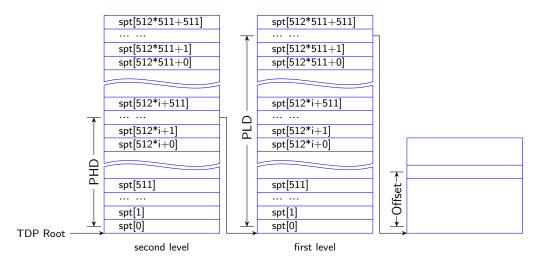

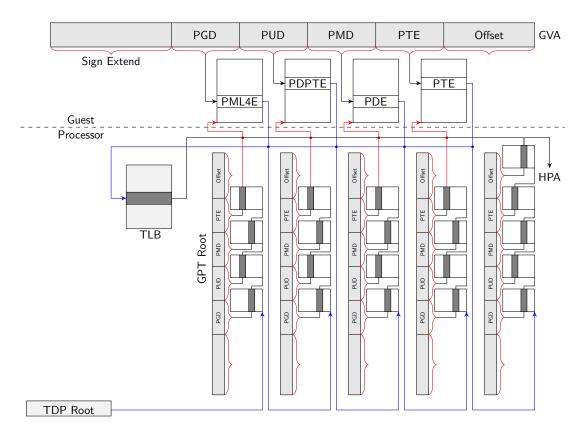

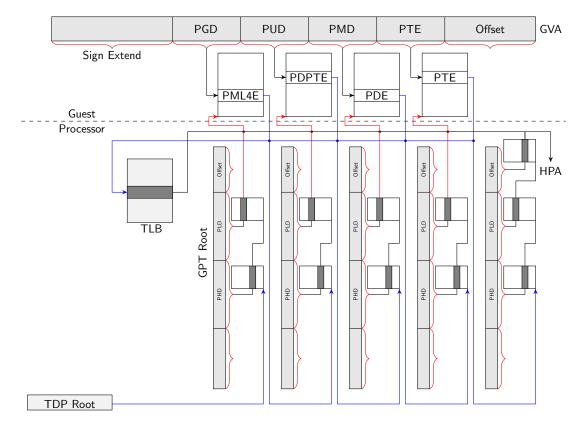

| 4.8          | The 2-level paging scheme for TDP                                                   |

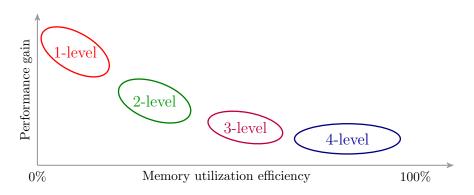

| 4.9          | Balance between performance and memory utilization efficiency                       |

|              | Restructured page table                                                             |

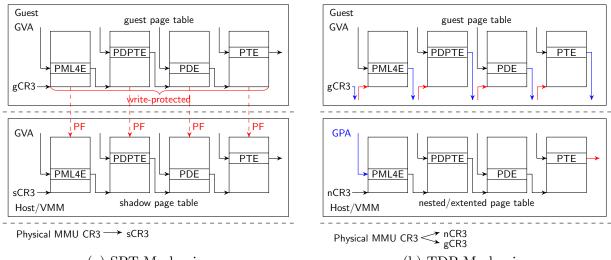

|              | Overview of the SPT and TDP mechanisms                                              |

| 4.12         | Two TDP schemes                                                                     |

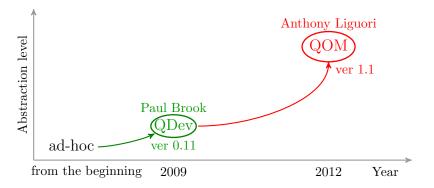

| 5.1          | Evolution of the QEMU Device Model                                                  |

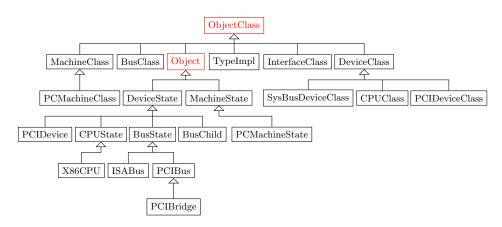

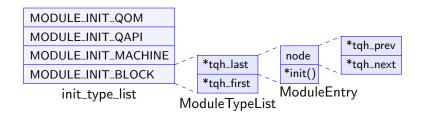

| 5.2          | Hierarchy formed by the entities in QOM                                             |

| 5.3          | Hash table used for managing the emulated devices                                   |

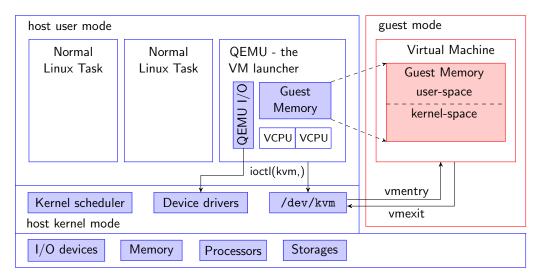

| 5.4          | QEMU and KVM as a whole hypervisor                                                  |

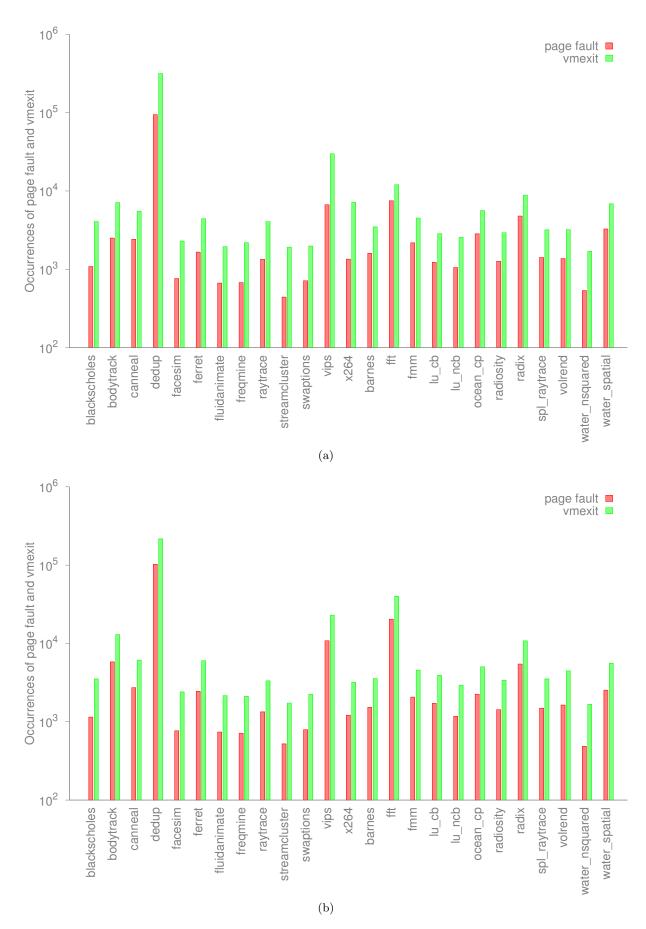

| 5.5          | Occurrences of page fault and vmexit for PARSEC-3.0 workload                        |

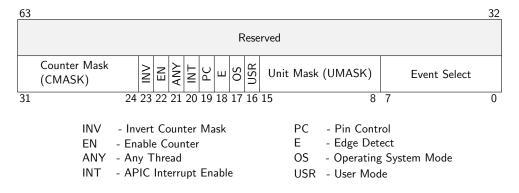

| 5.10         | Bit field layout of IA32_PERFEVTSEL MSR 70                                          |

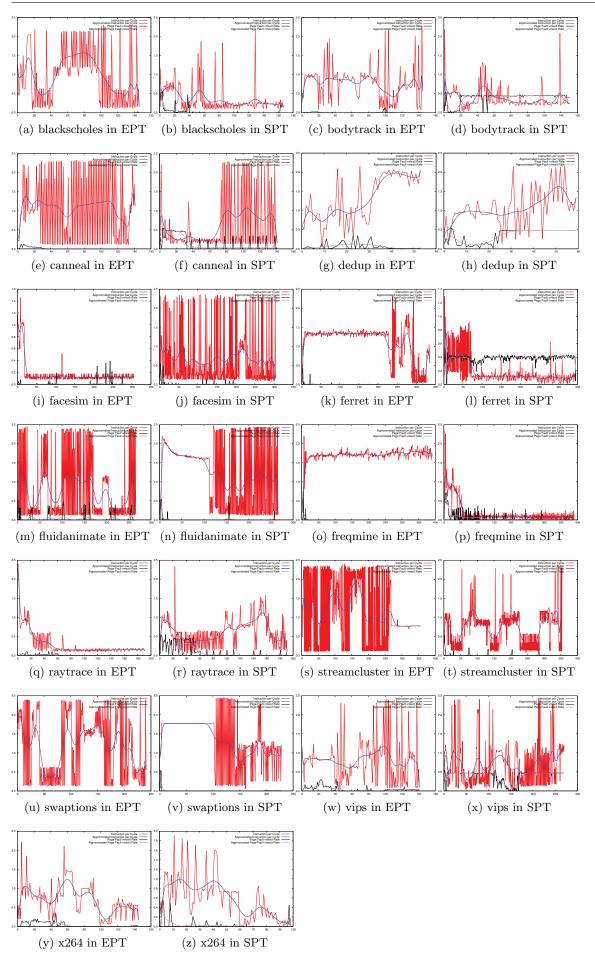

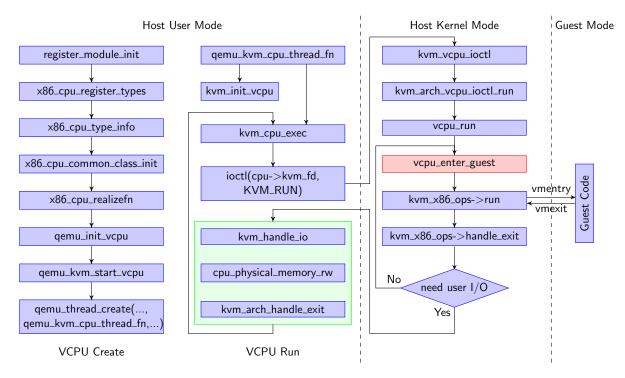

|              | Execution path of the QEMU-KVM hypervisor                                           |

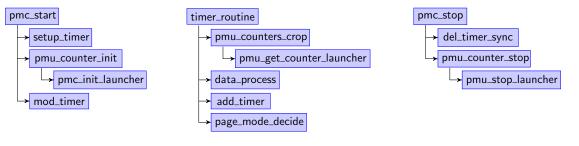

|              | Call chains formed by the APIs for PMCs control                                     |

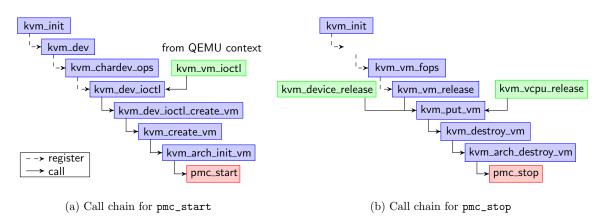

| 5.13         | Cascading call chain where PMC mechanism is integrated in                           |

| 5.15 | Data structure for the restructured page tables          | 82<br>84<br>86 |

|------|----------------------------------------------------------|----------------|

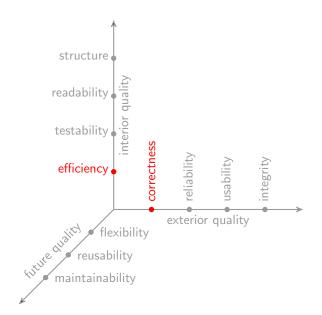

| 6.1  | Typical quality factors involved in software engineering | 90             |

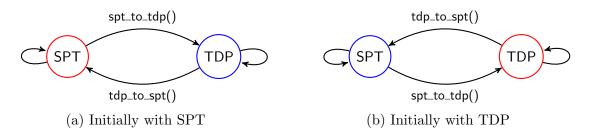

| 6.2  | Switching in four cases                                  | 92             |

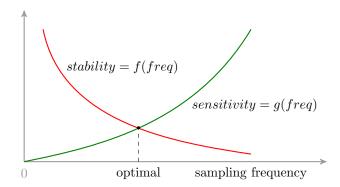

| 6.3  | Theoretical relation between stability and sensitivity   | 94             |

| 6.4  | Performance comparison among DPMS, SPT and TDP           | 96             |

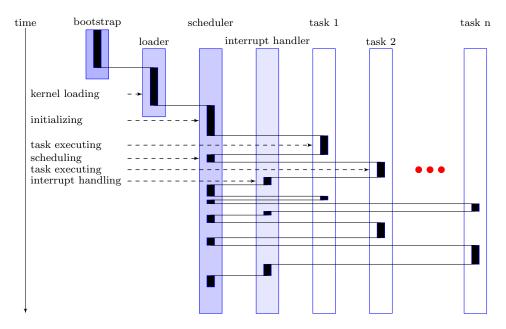

| 7.1  | Task scheduling and the associated kernel activities     | 98             |

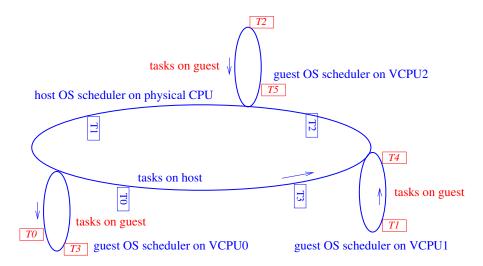

| 7.2  | Scenario for VCPU scheduling                             | 99             |

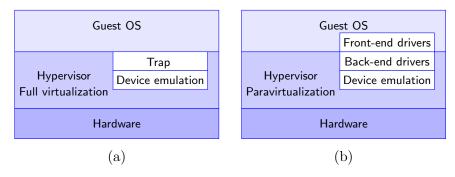

| 7.3  | I/O device emulation in full and paravirtualization      | 100            |

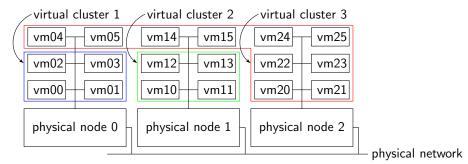

| 7.4  | Virtual clusters                                         | 105            |

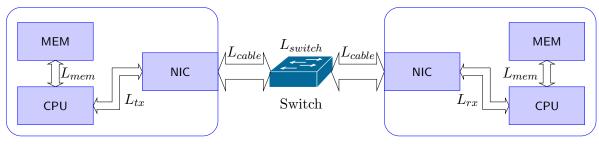

| 7.5  | Cluster used for benchmark                               | 106            |

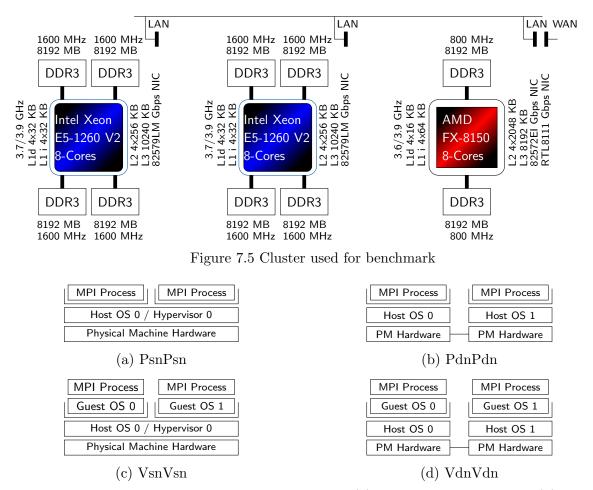

| 7.6  | Basic ways to run an MPI application                     | 106            |

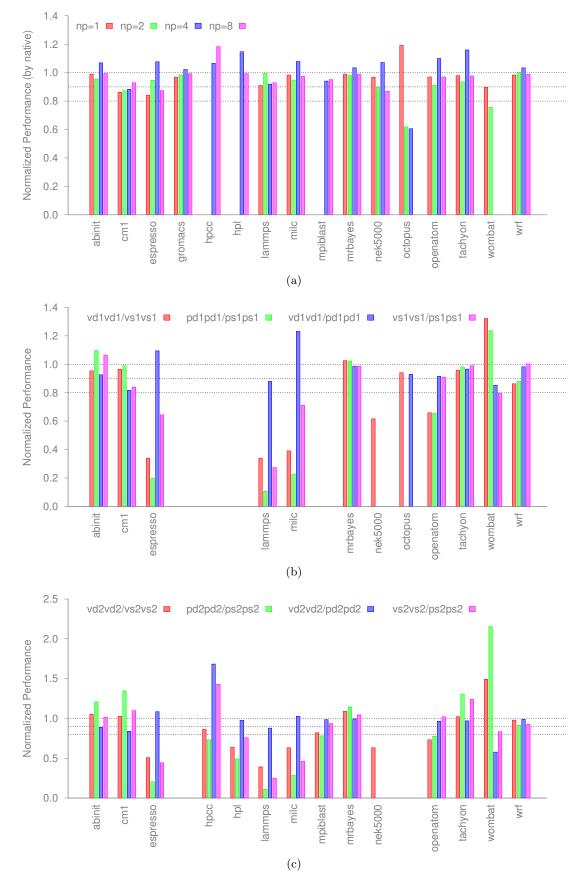

| 7.7  | Performance comparisons                                  | 109            |

# List of Tables

| 3.1 | A set of typical benchmark suites for performance research                                                          | 27  |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Performance comparison between the <i>shadow paging</i> and the <i>nested paging</i>                                | 32  |

| 3.3 | Summary of the results observed in benchmark                                                                        | 33  |

| 4.1 | A complete procedure and the cost for a GVA $\!\!\!\!\rightarrow \!\!\!\!$ HPA translation $\ldots \ldots \ldots$ . | 52  |

| 5.1 | A brief comparison of the QDev and QOM                                                                              | 58  |

| 5.2 | Major Functions implemented by KVM                                                                                  | 60  |

| 5.3 | Statistics of PARSEC-3.0 workloads on P1 and P2                                                                     | 64  |

| 5.4 | Allocation and configuration of PMC MSRs                                                                            | 71  |

| 5.5 | Format of the entry in level-2 table in the second dimension                                                        | 86  |

| 5.6 | Format of the entry in level-1 table in the second dimension                                                        | 87  |

| 7.1 | Performance Loss over Communication Network (normalized)                                                            | 107 |

# List of Abbreviations

| FLOPS                                | floating-point operations per<br>second |  |  |  |  |

|--------------------------------------|-----------------------------------------|--|--|--|--|

| MIPS                                 | millions of instructions per sec-       |  |  |  |  |

| ond                                  |                                         |  |  |  |  |

| NPT                                  | nested page table                       |  |  |  |  |

| VMM                                  | virtual machine monitor                 |  |  |  |  |

| ABI                                  | application binary interface            |  |  |  |  |

| AI                                   | artificial intelligence                 |  |  |  |  |

| API                                  | application programming inter-<br>face  |  |  |  |  |

| BIOS                                 | basic input/output system               |  |  |  |  |

| CFD                                  | computational fluid dynamics            |  |  |  |  |

| CFS                                  | completely fair scheduler               |  |  |  |  |

| $\mathbf{CMP}$                       | chip multi-processor                    |  |  |  |  |

| CPAIMD                               | Car-Parrinello Ab Initio Molec-         |  |  |  |  |

|                                      | ular Dynamics                           |  |  |  |  |

| $\mathbf{CPU}$                       | central processing unit                 |  |  |  |  |

| CUDA                                 | compute unified device archi-           |  |  |  |  |

|                                      | tecture                                 |  |  |  |  |

| DBT                                  | dynamic binary translation              |  |  |  |  |

| DDR                                  | double data rate                        |  |  |  |  |

| <b>DFT</b> Density Functional Theory |                                         |  |  |  |  |

| DIMM                                 | <b>1</b> dual-in-line memory module     |  |  |  |  |

| DPMS                                 | dynamic paging method                   |  |  |  |  |

|                                      | switching                               |  |  |  |  |

| $\mathbf{EC2}$                       | elastic compute cloud                   |  |  |  |  |

| EPTP                                 | extended page table pointer             |  |  |  |  |

| $\mathbf{EPT}$                       | extended page table                     |  |  |  |  |

| $\mathbf{FFT}$                       | fast fourier transformation             |  |  |  |  |

| FPGA                                 | field programmable gate array           |  |  |  |  |

| GPA                                  | guest physical address                  |  |  |  |  |

| GPGPU                                | general purpose graphic pro-            |  |  |  |  |

|                                      | cessing unit                            |  |  |  |  |

| $\mathbf{GPT}$                       | guest page table                        |  |  |  |  |

| $\mathbf{GPU}$                       | graphic processing unit                 |  |  |  |  |

| GUPS                                 | giga updates per second                 |  |  |  |  |

| GVA                                  | guest virtual address                   |  |  |  |  |

| HPA                                  | host physical address                   |  |  |  |  |

| HPDA                                 | high performance data analysis          |  |  |  |  |

| $\mathbf{HT}$                        | hyper transport                         |  |  |  |  |

| I/O                                  | input/output                            |  |  |  |  |

| IC                | integrated circuit             |

|-------------------|--------------------------------|

| IOMMU             | input output memory manage-    |

| 1011110           | ment unit                      |

| IPC               | instruction per cycle          |

| ISA               | instruction set architecture   |

| KVM               | kernel virtual machine         |

| LHP               | lock holder preemption         |

|                   | LINear equations software      |

|                   | PACKage                        |

| MMU               | memory management unit         |

| MPI               | message passing interface      |

| MPP               | massively parallel processors  |

| $\mathbf{MSR}$    | model-specific registers       |

| NFS               | network file system            |

| NIC               | network interface card         |

| NLP               | node-level parallelism         |

| NUMA              | non-uniform memory access      |

| NWP               | numerical weather prediction   |

| $\mathbf{OpenCL}$ | open computing language        |

| OS                | operating system               |

| PCI               | peripheral component intercon- |

|                   | nect                           |

| $\mathbf{PDE}$    | partial differential equation  |

| $\mathbf{PFN}$    | page frame number              |

| $\mathbf{PF}$     | page fault                     |

| $\mathbf{PGD}$    | page global directory          |

| PHD               | page higher directory          |

| PLD               | page lower directory           |

| $\mathbf{PMC}$    | performance monitor counter    |

| PMD               | page middle directory          |

| PTE               | page table entry               |

| PTPC              | page table pointer cache       |

| PUD               | page upper directory           |

| PVM               | parallel virtual machine       |

| PWC               | page walk cache                |

| QOM               | QEMU object model              |

| QPI               | quick path interconnect        |

| REML              | restricted maximum likelihood  |

| $\mathbf{RMS}$    | recognition, mining and syn-   |

| DVI               | thesis                         |

| RVI               | rapid virtualization indexing  |

| SLL              | shared last level               | TLP                    | thread level parallelism        |

|------------------|---------------------------------|------------------------|---------------------------------|

| $\mathbf{SMP}$   | symmetric multiprocessing       | $\mathbf{TMR}$         | TLB-miss rate                   |

| SR-IOV           | single root input output virtu- | $\mathbf{USB}$         | universal serial bus            |

|                  | alization                       | VALE                   | virtual local ethernet          |

| STDP             | simplified two dimensional pag- | $\mathbf{VCPU}$        | virtual central processing unit |

|                  | ing                             | VirtIO                 | virtual input and output        |

| $\mathbf{SVM}$   | secure virtual machine          | VMCB                   | virtual machine control block   |

| $\mathbf{TDDFT}$ | time-dependent density func-    | VMCS                   | virtual machine control struc-  |

|                  | tional theory                   |                        | ture                            |

| TDP              | two dimensional paging          | $\mathbf{VMD}$         | visual molecular dynamics       |

| TLBM             | translation lookaside block     | $\mathbf{V}\mathbf{M}$ | virtual machine                 |

|                  | miss                            | $\mathbf{VR}$          | virtual reality                 |

| $\mathbf{TLB}$   | translate look-aside block      | $\mathbf{VT}$          | virtualization technology       |

## Chapter 1 Introduction

#### Contents

| 1.1 | Backg  | round                                                                                                                        |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------|

|     | 1.1.1  | HPC and its Major Concerns                                                                                                   |

|     | 1.1.2  | System Virtualization                                                                                                        |

|     | 1.1.3  | Exploit Virtualization in HPC                                                                                                |

| 1.2 | Probl  | $em Description \ldots 10$ |

| 1.3 | Thesis | S Contribution to the Current Research                                                                                       |

| 1.4 | Outlin | e of the Thesis                                                                                                              |

This chapter provides the background, describes the problem, the contributions and the outline of this thesis. First, high performance computing (HPC) is briefly introduced with the focus on its major concerns. Then, the system virtualization technology is introduced to address such concerns posed in the evolution of HPC. However, the adoption of this virtualization technology in HPC has also problems, of which the performance loss is the major one. This thesis focuses on the performance loss in guest memory address translation and attempts to work out solutions for this problem.

## 1.1 Background

#### 1.1.1 HPC and its Major Concerns

High performance computing has been around for a few decades. This is a branch of computing that tackles the most complex and challenging problems arisen in science and engineering. By solving fundamental research problems with HPC, human makes scientific discoveries and pushes forward the frontier of knowledge. As a powerful tool for research and production, HPC makes use of the cutting-edge hardware, therefore represents the most high-end computing technology. Breakthroughs achieved in HPC may also benefit other branches of the computing community. In this sense, HPC is a key area and has potential significance for computing as well as a broad range of science and technology.

From a technical perspective, the transformation from monolithic mainframes to cluster-based supercomputers is a major breakthrough in the development of HPC system. While this enables more flexible way of construction, a scalable performance and a lower investment for the facility, the growing model for the HPC systems is increasingly meeting serious challenges. Generally, challenges may be posed by the following concerns about an HPC system:

#### Performance

Intrinsically, the performance of a computer is generally understood as the speed achievable by the computer in accomplishing tasks. For a workload with fixed amount of task, performance can be indicated by the execution time. The longer the execution time is, the lower the performance will be, hence the relation  $^{1}$ ,

#### performance = 1/execution time

Performance is not only a major concern in computing, but also the key driving force behind the advance in computer architecture [1] and the primary target for computer design. A great deal of efforts are dedicated to the study of performance in computer architecture.

Depending on the purpose of research, the performance of a computer can be measured for the whole system, such as the LINPACK results for a supercomputer or for an individual component. The result can be either an absolute figure indicating the performance of a given hardware and software or a ratio for comparing the influence due to different systems or different configurations for the same system.

From a system engineering point of view, performance is a non-functional quality but depends on many functional qualities. According to Dongarra et al., "the performance of a computer is a complicated issue, a function of many interrelated quantities" [2]. These factors embrace a broad range of issues in hardware and software, including:

The frequency of processor cores, the size, level of caches, the size, level, and associativity of TLBs, the frequency, size of memory chips, the bandwidth and latency of the network card, the frequency of memory bus and PCI bus, the volume and speed of storages, the size of the program, the programming language and algorithm the program applies, the compiler's capability for code generation and optimization, the static and dynamic libraries, the operating system, the organization and architecture of the computer or computing system and so on.

The overall performance of an application is determined by the interaction between the entire instructions and the underlying hardware.

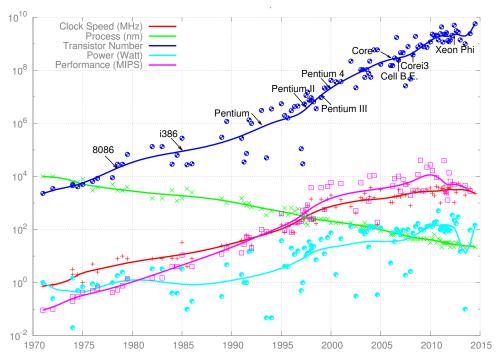

As a result of the enhancements in circuit and architecture technology, processor, memory and I/O devices saw unprecedented increase in speed and capacity. Figure 1.1 depicts the evolution of processors in the past few decades. Alongside with the decrease in process and in power (energy consumption per time unit) is the exponential increase in clock speed (frequency), number of transistors per die, and speed of instruction execution (performance). Since the flourishing of microprocessor and the integrated circuit (IC) industry, these trends accord with a famous "rule of thumb" - the *Moore's law*, which predicts that the number of components per integrated circuit doubles approximately every two years. According to Intel's former executive, David House, the processor chip's performance would double every eighteen months, as a resultant of both the increased number of transistors, and the enhanced speed of them [3]. The prediction proved fairly accurate during the past decades. However, in the recent decade, the shrinking of transistor size is almost approaching the atom scale, posing physical barrier for further shrinking.

While there are discussions about the effectiveness of the *Moore's law* as the general roadmap for semiconductor industry in the future [5], processor has begun to follow the multi-core approach to continue growing its performance by adopting spatial redundancy of the hardware. Although the clock speed comes to a stagnation, the theoretical performance can still be scaled by the number of cores. This becomes the main reason why the *Moore's law* still holds true in a multi-core era. Such an architectural change has a fundamental impact on the way of processor utilization. To make effective use of the parallel hardware, software have to be developed in a parallel and multi-core approach, instead of the traditional sequential and uni-core approach. The actual performance and effective utilization lie in the scalability of the software across cores.

From a system point of view, not only the processor, but also the other computer components, as well as the architecture innovations have contributed to the performance growth. In addition to the multi-core technology, the following architectural technologies also push forward the overall performance [1]:

<sup>&</sup>lt;sup>1</sup>In practice, other notations such as the number of floating-point operations per second (FLOPS), or millions of instructions per second (MIPS) are also used.

Figure 1.1 Evolution of the processors [4]

- Pipelining and super-pipelining

- Multiple levels of cache memory

- RISC architectures

- Multiple execution units (single data, multiple instruction)

- ISA extension (to take advantage of single instruction, multiple data)

In the recent decade, additional novel technologies continued boosting the overall performance of the computer and computing system, including [1]:

- Multithreading (super-/hyper-threading to exploit the *thread level parallelism*)

- Speculation and prediction mechanism (to take the advantage of idle execution units)

- Hardware accelerating (inside and outside the processor chip)

- Vector and array processing

- Large-scale parallel and distributed computing

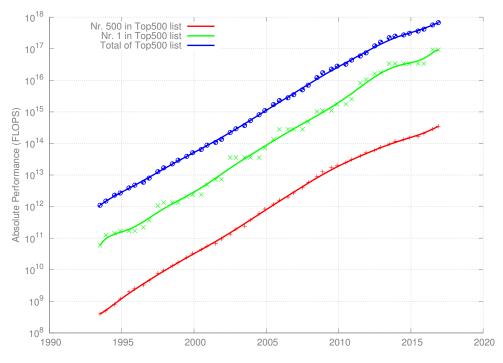

Figure 1.2 illustrates the performance growth of the most powerful computing systems in the world, the top 500 supercomputers, since the flourishing of HPC industry. The performance of the top one system has seen a growing from tens of GFLOPS to tens of PFLOPS, and is looking forward to EFLOPS (exascale<sup>2</sup>) era.

## Power Consumption and Efficiency

Despite the steady technical advances in processor and architecture, the expansion in dimension still remains as a major source of performance growing. While large-scale parallel and distributed system emerge as the popular computing architecture and the power consumption per processor (core) is decreasing, the power consumed by the whole system is still tremendous. Power consumption and power efficiency become increasingly a concern since a decade ago. Nowadays they are emerging as the critical limiting factors for high performance computing.

<sup>&</sup>lt;sup>2</sup>exa is a prefix denoting a factor of  $10^{18}$ .

Figure 1.2 Growth of the supercomputer performance [6]

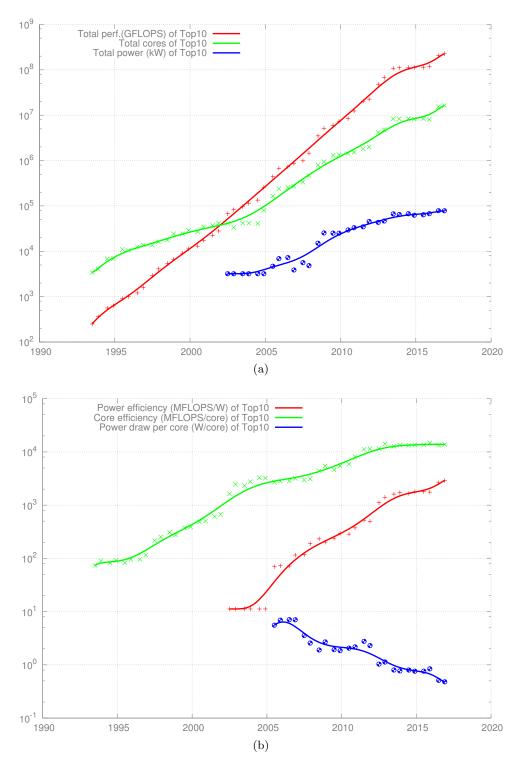

Supercomputers or HPC clusters consume energy not only for computing, but also for cooling to prevent the hazard of excessive heating. Power supply and budget add heavy burden to the computing industry. Such a developing model is unhealthy and unsustainable in the long run. Figure 1.3(a) depicts the evolution of the top 10 fastest supercomputers among the top 500 list since an early age from total performance, total number of cores, and total power aspects. These had undergone rapid growth and currently reached magnitudes unimaginable in daily life. While the total performance is approaching exascale by using tens of millions of cores, the total power is amounting to hundred Megawatts ( $10^6$  Watts), roughly 0.44% of the installed electrical capacity in the world's currently largest hydro-electrical power station<sup>3</sup>.

Figure 1.3(b), on the other hand, depicts the efficiency aspects in the same course. Efficiency refers to the ratio of output and input. The power efficiency, core (hardware) efficiency, as well as the "power draw per core" are compared over a relatively long period of time. Power efficiency measures the number of floating-point operations per watt, which has reached at a level of 2.8966 GFLOPS for the top 10 supercomputers. It is about 31.61% of the currently most power-efficient system (NVIDIA DGX-1, 9.4621 GFLOPS [8]). "Power draw per core" measures power consumption per processing unit (core) and indicates the current technical status for energy saving in processor design and manufacture. In the past decade, this has been reduced to a level of 6.81% than at the early age (7.05 W/core in June, 2006, 0.48 W/core in November, 2016). This contributed enormously to curb the drastic growth of power demands for the entire computing industry over the past decade.

<sup>&</sup>lt;sup>3</sup>Three Gorges Dam, currently the largest hydro-electric power station, and the largest power producing body ever built, has an installed electrical capacity of 22,500 Megawatts [7].

Figure 1.3 Performance, power, scale of supercomputers (a) total amount, (b) efficiency [6]

### Hardware Utilization and Efficiency

Figure 1.3(b) also depicts the core (hardware) efficiency, which has increased by a magnitude of two orders since the initial stage of high-performance computing industry. As this is the average of all types of the concerned processing units, it represents the general growing trend of the HPC technology. In the recent years, the core (hardware) efficiency reached a plateau after climbing a slope, implying that the performance is roughly proportional to the number of cores (the scale of computing system). To limit the computing system within a reasonable scale, the strategy is to increase the "performance per unit chip area".

Another concern is the hardware utilization. Since long ago, computer, especially the servers in large data centers are plagued with the underutilization problem, which prevents the effective use of the resources and lowers the profits in production. The server farm in a data center, for example, may suffer huge profit loss due to insufficient utilization of resources. Owners of such infrastructures are in a dilemma. As reliable service providers, they are expected to maintain higher availability of their services, at best 100% of the time without any downtime. On the other hand, the influx of workloads may fluctuate from time to time, thus is unpredictable. The workload may be distributed unevenly among servers, which creates load imbalance from server to server. The consequence is that even the underutilized or idle servers had to stay powered on, with less or no productivity at all. Studies indicate that a typical server is estimated to have 8% to 30% of its uptime for running applications on average, with the rest portion of time simply wasted by running idly (Gartner Group)[9]. Similar thing occurs in companies with production servers. It is estimated that on average 15% of the full-time servers in such companies perform no useful tasks [10], leading to a huge waste of both hardware and energy worldwide.

In high-performance computing, underutilization problem seems not to be acute as that in case of servers of data centers. This is probably due to the fact that HPC has much smaller user groups that generate dedicated tasks in a more homogeneous way. However, since the supercomputer carries a huge permanent investment but has much shorter life-span than normal servers, its utilization tends to be calculated by the unit of "node hour". Idle and underloaded states of the system simply mean lower production, lower economic efficiency, and add the cost per-unit of service the system provides. In this sense, higher utilization of the hardware resources means cost saving and economy promotion for high-performance computing.

#### 1.1.2 System Virtualization

#### **Overview of Virtualization**

In computer science, a *virtual object* is a concept used to refer to a kind of logical entity created on the basis of the real physical entity. According to the definition by Popek and Goldberg, "a virtual machine is taken to be an *efficient*, *isolated duplicate* of the real machine." [11] Virtualization refers to the act of creating a virtual (rather than actual) entity, such as virtual computer hardware platforms, storage devices, and computer network resources [12]. Its purpose is to extend or replace an existing interface to mimic the behavior of another system [13].

In practice, virtualization may occur at several different levels in accordance with the abstraction layers in the architecture of a computer, such as hardware level (ISA), operating system level (ABI) and library level (API) [14]. System virtualization is the virtualization at the hardware level. The entity to virtualize is the entire hardware of a computer.

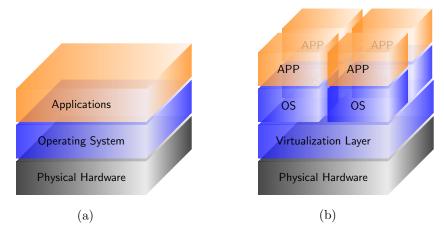

One effect that system virtualization creates for computer architecture is illustrated by Figure 1.4. Virtualization enables the *decoupling* between the OS and the hardware, as well as that between the applications and the OS. These are the bases for almost all other features.

Although the concept of virtualization and especially of virtual machines were in the focus of computer scientists and engineers in the recent two decades, their origins go back to the first generation of computers in the 1960s [15]. Due to the prohibitive-high prices and a centralized, non-interactive way of using the mainframe computers, the expensive computing resource tended to suffer from underutilization problem. A variety of time-sharing, multi-tasking, multi-user systems were created to boost the resource utilization and ease the use. Virtual machine comes as a more advanced variant of that technology. System resource can be partitioned into independent fine grains and assigned to multiple users running multiple tasks in an encapsulated, isolated way. This is an excellent feature, which makes virtual machine quite useful for boosting the computer system resource utilization. Furthermore, more benefits are also brought by virtualization for computing, including:

Figure 1.4 System virtualization (a) traditional architecture, (b) virtual architecture

### Virtualization's Benefits

- **Better customization** The nature of encapsulation and isolation permit customizable execution environment for the user applications.

- **Higher scalability** Physical servers can be set up easily by rapid and dynamic provision. Deploying a new virtual machine is as easy as copying a file. The whole computing system becomes much more scalable by adding or removing virtual machine guests.

- **Higher flexibility** Workload on a physical machine can be migrated, check-pointed, resumed. Even the virtual machines can be reconfigured dynamically. New workloads can be deployed more quicly and conveniently than on physical machines.

- **Higher security** As workloads in one virtual machine are encapsulated and isolated in a single execution environment, malicious attack or accidental mishap in one virtual machine cannot propagated to other virtual machines or bring down the whole physical machine.

- Less hardware and energy cost The same amount of task performed by a number of virtual machines results to a reduced amount of physical hardware as well as power consumption.

- Less deployment effort Physical servers can be quickly loaded by standardized virtual machine image (VM provisioning).

### Virtualization's Limitations

Despite the potential benefits and competitiveness virtualization brings for computing, the adoption of virtualization for computing has also problems. Taking the data center, where the virtualization technology is widely adopted, as an example, the whole system is inevitably complicated due to the presence of a virtualization layer.

A system consisted of both physical and virtual infrastructures also pose great challenge to the hardware and maintainer. According to a number of representative articles [16, 17, 18] by IT professionals, analysts and vendors, the major challenges faced by data centers are the following:

• VM sprawling Originally the use of virtual machine were intended to reduce the number of physical servers in data center. However, probably due to the convenience and low cost of deploying virtual servers, benefits are eroded by the overgrown virtual servers in the course of poorly planned VM life cycle and placement. Storages may be depleted quickly by many less-used VM images. Network switches get saturated by the unplanned overwhelming data traffic floods among virtual servers. Network becomes complexed and too often dynamically reconfigured by the virtual network switches. Troubleshooting becomes harder in multiple-layer virtual environments. The physical servers will be overburdened by carelessly launched migration and consolidation. Consistent security policy is more difficult to be enforced in an infrastructure composed of physical and virtual servers.

- Physical and geographical restrictions For the VM migration and server consolidation, virtual environment places more restrictions on hardware. For example, server hardware for migration purpose should have some special features such as identical PCI and NIC supports. A data center is expected to situate within a maximum distance to the neighboring one as the source or destination for migration. So sufficient bandwidth and latency can be ensured.

- Lack of standard and interoperability among vendors of hypervisors For data centers, hypervisors play the central role. Although VMware platform is still dominating the x86 server virtualization, it is increasingly common to find out data centers based on other hypervisors such as Citrix XenServer [19], Red Hat KVM [20], or Microsoft Hyper-V [21]. Various vendors apply their own management tools for task and resource controlling. But few of them take care of the interoperability with products from other vendors. Instead they normally come up with features which may not be available for hypervisors from other vendors. Maintainers need more efforts to get used to different platforms.

- Lack of freedom to move between x86 processors Although the two major x86-based processor vendors Intel and AMD share the same ISA, the implementations of the ISA have subtle differences, which leads to different behavior for a few instructions. Furthermore, each of them had also come up with their own virtualization extensions. The hypervisor developers need to provide vendor-specific solutions for both Intel and AMD processors. While this poses no problem for VM "cold" migration, it does so for VM life migration.

- Vulnerability at storage and network switches A data center is a large array of servers. The SAN (storage area network) and network switches bear the stress of data flow among a large number of physical and virtual servers. This makes them easy to get stuck or congested by data floods. Centralized components like the storage and network are by nature vulnerable to the high I/O traffic throughput.

- **Obscured virtual server security** To maintain the illusion of transparency for end-users, all physical and virtual servers need to have their identifications somewhat merged in a cloud environment. Therefore, the entities and environments become more dynamic, fluid and volatile. The boundary for security in the infrastructure may be blurred. Not only the physical layer, but also the virtual layer needs to be patched when necessary.

- Software license impact For the data centers running commercial hypervisors, the license could be an important consideration. Not only for the huge amount of charge, but also for the strong impact on the virtual infrastructure delivered by the license terms and pricing models. Taking the VMware product, vSphere<sup>4</sup>, as an example [22]. The vSphere version 4 license charge is based on a combination of physical processor cores, sockets, and physical memory volume installed on the server, with 1 socket, 6 cores, and 256 GB memory as the standard charging level. In contrast, the version 5 standard changed to a pricing model based on virtual rather than physical memory and allows a total of only 24 GB to allocate to all VMs, and up to 8 VCPUs per VM. While the former version encourages "scale-up", running as many VM guests as possible on a system with fewer sockets but more memory, the latter penalizes this way by "scale-out", purchasing more physical servers each with far less physical memory. A single move in license terms has actually led to a three times higher price than previously. This has driven many of the VMware customers to abandon the vSphere and turn to Citrix XenServer or Microsoft Hyper-V.

- Degradation of the performance Last but not least, virtualization may suffer more or less native performance. By empirical research in early years [23], a rough estimation of the performance for the major components in a virtual execution environment is: CPU 96-97%, Network 70-90%, and Disk 40-70% of the native performance. Although this estimation is made over a decade ago and may not reflect the current status, large performance loss is still not uncommon for virtualization.

<sup>&</sup>lt;sup>4</sup>VMware vSphere is a softwares package, including vSphere client, vCenter server and ESXi hypervisor.

#### 1.1.3 Exploit Virtualization in HPC

The concerns mentioned in Section 1.1.1 exist commonly in the computing community, especially where large-scale IT infrastructures are used. High performance computing is not an exception. As the hardware facility is expanding, problems such as the resource underutilization, excessive power draw, and system management are posing increasingly as challenges for the HPC systems. The adoption of virtualization technology enables the HPC to abstract, pool and automate the resources so as to overcome such challenges due to the rigid physical limits in the HPC systems.

This makes sense especially considering that HPC is increasingly demanded by new groups of users other than research area. As a result, HPC systems are growing more commercial and more business-oriented. In such situation, business agility and enhanced security become urgent issues to deal with multiple non-trusted users. Virtualization's benefits for computing lie in:

#### **Customizable Execution Environment**

The virtualization technology's competence is basically rooted in its capability of reducing the strong dependency between the system software (OS) and the underlying physical hardware, as well as the strong dependency between the user application software and the system software.

Physical hardware, precisely the processor, is characterized by its ISA, the interface with the software. The software targeted at a given hardware platform must comply with the form of hardware's ISA. Similarly, an OS is characterized by its system calls, the interface with user applications. Applications need to comply with the system calls of the given OS for execution. These dependencies are known as *tight coupling*. Constrained by this, a server can be installed with a single OS only, thus bound to run application software only for the same type of OS and processor architecture. Such a bound leads to the "one server, one application" model.

Adoption of virtualization on the server platform has effectively broken these *tight couplings* and fundamentally changed this model. By inserting the hypervisor – an indirection layer between OS and hardware, a server (physical machine) acquires the capability of running multiple OSes (virtual machines) concurrently. Each of these virtual machines is isolated from each other and encapsulated as an independent execution environment. By deploying virtual HPC clusters in the supercomputer environment, the software stack for execution environment may achieve higher capability to be reconfigured or customized on demand of the users.

#### System Resource Utilization Enhancing

The "one server, one application" model constrains the service providers to put a single workload on a server for reliability and quality of service (QoS) reasons. Server is equipped with abundant computing resources for running multiple tasks. By multiplexing the computing resources among a reasonable number of virtual machines guests, the physical server gets sufficient tasks to stay busier and more productive. Each VM guest may be dedicated to a specific service as if it were a physical server.

The number of guests is known as *density*. Too small density brings quite limited increase in utilization. While too large density may saturate the physical server and degrade the quality of services in guests. A properly chosen density keeps the server reasonably loaded, meanwhile does not necessarily incur visible damage to the quality of service in each guest. By virtualizing physical server, productivity of the computing resource can be increased by exploiting idle time.

#### Power and Hardware Efficiency Enhancing

With virtualization of the computing resources, physical nodes in a supercomputer (HPC cluster) may be used by loading a number of VM guests as the virtual computing nodes. More than one applications are allowed to run concurrently in the single host. Due to *decoupling*, a virtual node is not bound to any physical node. An execution environment presents itself as a file stored

in hard disk or in memory, which is fairly easy to move from physical node to physical node via interconnect network, either by copying a static file on a disk (static migration) or a file on a disk together with the image in memory (dynamic migration). Load balance is achieved by migrating virtual nodes from overloaded physical nodes to underloaded physical nodes while power can be saved by migrating those sparsely spreading virtual nodes to fewer physical nodes, and powering off the rest (known as the VM consolidation). Both the hardware and power are utilized more productively, which enhances their efficiencies compared to physical case.

### **1.2** Problem Description

Traditionally, virtualization technology is not oriented to workloads that are resource-intensive. Hypervisor is optimized mainly for the domains where workloads have moderate and predictable demand for resources.

Among the barriers for adopting virtualization in HPC, performance loss is a major consideration [24, 25, 26, 27]. Among factors that incur performance loss of the HPC workload due to virtualization, memory address translation is a potential bottleneck [28], especially for workloads that are memory-intensive and exhibit unusual run-time behaviors. In dealing with the diverse HPC workloads, the currently adopted two standard solutions, *shadow paging* and *nested paging* for translating the VM guest memory address have the following limitations: 1) guest workloads are treated in the same way, despite their various characteristics and significantly different run-time behaviors in memory-accessing; 2) the default memory address translation way is not optimal when performance comes as the top priority.

Due to these limitations, the guest memory virtulization may not be optimized to yield nonnegligible performance loss for a given workload in the guest. Research [29] indicates up to 40% of performance degradation for the memory intensive workloads (PASSMARK MEMORY) in the XenServer 5.5 HVM environment.

The goals of this work are: 1) To investigate the performance loss of typical HPC workload in virtualized execution environment due to guest memory virtualization; 2) To work out solutions to improve the performance of the typical HPC workload in virtualized execution environment.

## **1.3** Thesis Contribution to the Current Research

This research presents two solutions to work around the limitations for virtualizing the guest memory address translation. Namely, they are **DPMS** (dynamic paging method switching) and **STDP** (simplified two-dimensional paging), as elaborated below:

- 1. **DPMS** Overcomes the first limitation stated in Section 1.2. With this, the hypervisors can adjust its paging method for translating the guest memory address based on the decision made during the running of the guest applications. DPMS brings a new feature to the hypervisors, which enables hypervisors to react to the ever-changing behaviors exhibited by the running workload with an adaption to the optimal paging method. Workloads with different characteristics can be handled differently based on their run-time behavior in memory accessing. In this approach, the performance of the diverse HPC workloads, especially those memory-intensive workloads will be benefited.

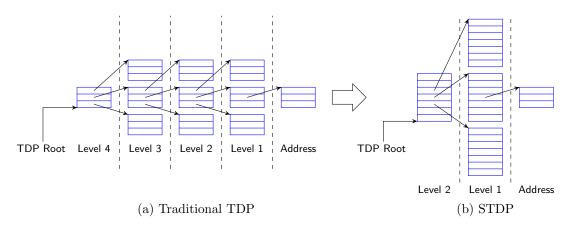

- 2. **STDP** Overcomes the second limitation stated in Section 1.2. STDP is variant of the traditional TDP. As the bulk of the TDP overhead lies in traversing page tables in the seconddimension, to reduce the overall page-table walking overhead, a fundamental way is to adopt fewer level page tables in the second-dimension. STDP is therefore prompted as an innovation of the current TDP supported by both the hypervisor and the hardware processor. Without considering the TLB, STDP is able to reduce 40% to 60% of the paging overhead in the second dimension, which is a big advantage compared with the current TDP.

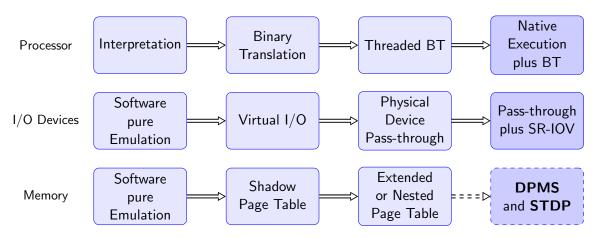

In a broad view, the thesis contribution is presented by the last row of Figure 1.5, which depicts the road map for the evolution of the system virtualization technology. Till now, the technology for virtualizing each component of a physical computer has undergone a few generations.

A fact identified is that in each generation, virtualization losts a part of virtualization in its essence. In other words, except for a few core functions which make virtualization "virtual", a significant portion of the functionality has been taken over by the bare-metal hardware. From the software-based pure emulation to the binary translation, to native execution of the instructions with occasional binary translation, from the software-based pure emulation to para-virtualized VirtIO to physical device pass-through, the performance for both the processor and I/O device virtualization gain impressive progress.

BT: binary translation; SR-IOV: single-root input/output virtualization

Figure 1.5 Problem domain on the road map of virtualization's evolution

In contrast, the potential breakthrough for memory virtualization occurs with the adoption of *nested paging*. However, despite the advantage over *shadow paging*, *nested paging* has also drawback. In this sense, the current *nested paging* serves as an alternative, but not yet an entire replacement of *shadow paging*. What is the next generation technique for memory virtualization parallel with the breakthroughs for both processor and I/O device virtualization?

For these reasons, the major efforts of this work are dedicated to memory virtualization, with a focus on how to improve the current solutions for such a narrow topic in the big picture. These efforts lead to the contributions mentioned above.

## 1.4 Outline of the Thesis

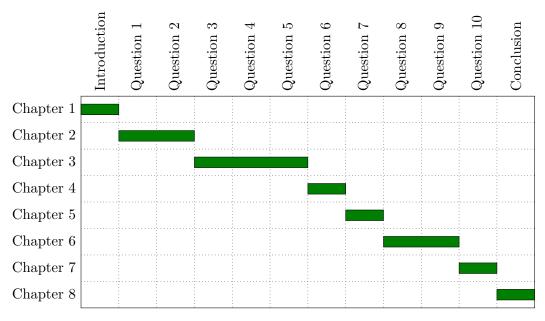

The thesis is organized like this: Chapter 1 presents the background and describes the research problem. Chapter 2 reviews the current related work in this area. Chapter 3 is engaged in seeking the performance drawbacks with a series of benchmarks on different testing platforms. Based on these results, Chapter 4 proposes two solutions for improving the hypervisors for HPC workloads. Chapter 5 works out an implementation for the proposed ideas based on a concrete hypervisor, QEMU-KVM. With the purpose of verifying the feasibility, Chapter 6 presents the results for a series of functional testing and performance benchmark. In Chapter 7, parallel with the major contributions in guest memory virtualization, efforts on the performance loss due to the processor and I/O virtualization are also mentioned. And finally, in Chapter 8, benchmark, design and implementation are concluded.

The thesis is outlined by a sequence of concrete questions below:

- 1. What is the current situation for using virtualization technology in HPC area?

- 2. What impact does virtualization deliver to the performance of HPC execution environment?

- 3. Which virtual execution environment may serve as an ideal platform for this research?

- 4. Which applications can be used to characterize HPC workload?

- 5. Which component of the virtualized system incurs acute performance issues?

- 6. What strategies, or measures can be proposed to remedy this?

- 7. How to implement these strategies in the context of a concrete hypervisor?

- 8. What is the effect of these proposed solutions?

- 9. How can these solutions be applied in related area?

- 10. What limitations do the new solutions have, and what can be done for further progress?

Figure 1.6 shows how the chapters are related with these questions.

Figure 1.6 Outline of the thesis

## Chapter 2 Related Work

#### Contents

| <b>2.1</b> | System Virtualization                 | 13        |

|------------|---------------------------------------|-----------|

| 2.2        | Virtualization in HPC                 | 17        |

| <b>2.3</b> | Performance for Memory Virtualization | <b>21</b> |

| <b>2.4</b> | Summary                               | 23        |

This chapter sketches the topography and frontiers of the research area by exploring the related works. Section 2.1 reviews the current status for system virtualization technology. Section 2.2 examines how virtualization technology is utilized, and to what extent it has influenced the development of HPC. Section 2.3 surveys the efforts that are dedicated to the performance aspect of the memory virtualization in both the traditional and the virtualized execution environments. It particularly focuses on achievements and limitations for the major contributions in improving the virtualization of the guest memory address translation process. Finally, Section 2.4 draws a summary of the reviewed related work, which presents a clear view of the current work, and the context to this thesis.

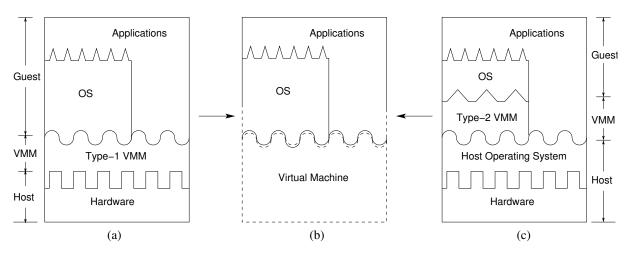

## 2.1 System Virtualization

System virtualization [14] provides the capability of creating multiple execution environments (OS plus user applications) simultaneously on a single set of physical hardware. Corresponding to the implementation of virtualization layer, hypervisors<sup>1</sup> roughly fall into two types: type-1 and type-2 [30], as Figure 2.1(a) (c) depicts, respectively. At the time when the trend for virtualization took off, type-2 hypervisors were the most popular form, mainly due to the convenience of turning the underlying physical machine into a virtual machine by installing the type-2 hypervisor on the available OS. However, type-2 hypervisors have a few downsides, primarily in performance, which is the reason for the emerging of type-1 hypervisors. This type of hypervisors runs on the bare-metal hardware as an OS, rather than as an application in the user-space. Therefore it can assume full control over the physical hardware and ensure higher performance, availability and security than the type-2 hypervisors.

Regardless of the hypervisor type, the execution environment presented by the virtualization layer is a virtual machine for the guest OS and the applications running inside. Figure 2.1(b) depicts this effect, a virtual machine that hides details of the real execution environment. The difference is almost unperceivable by the guest.

As the engine of virtual machines, the hypervisor abstracts and multiplexes the physical hardware among guests. The hypervisor is a piece of software to create virtualization by presenting an illusion to the guest OS atop, as if they were running in a bare-metal hardware environment. Controlled by the hypervisor, multiple guest operating systems can coexist and execute simultaneously to exploit the same physical hardware by hosting their own applications. Determined

<sup>&</sup>lt;sup>1</sup>Hypervisor is also known as the virtual machine monitor (VMM). They are often used interchangeably.

by the nature of each individual component, a computer applies a number of virtualization techniques. The virtualization techniques for the major components are examined below:

Figure 2.1 Stack layout of the virtual machine [14]

**Processor:** In the host, the processor is the central part and the primary target to virtualize. By nature, a processor is a device sharable in a temporal way among its tasks. In the traditional physical machine, a processor is utilized by running a specific task within a period of time (time slice). To support virtualization, processor can be virtualized by a number of approaches. Originally virtualization takes the form of emulation [31], which is able to run an unmodified OS and applications targeted to an architecture other than that of the underlying physical processor. The emulation belongs to virtualization in a broad sense, but is significantly different from the current virtualization approaches in many aspects. To run the software for non-native ISAs, the *instruction interpretation* and *binary translation* approaches are adopted. In emulations of these kinds, the physical processor is actually not emulated at the circuit or micro-architecture levels, but at the ISA level. The instructions of the source software are unable to execute on the underlying (target) platform. These approaches enable the semantic to be extracted from the source software and be reconstructed for the target ISA. Thus the software can execute on the target platform. Emulation is the most intuitive form of virtualization. The major problem is the poor performance due to *code expansion*<sup>2</sup>[32]. On average, a ratio of 1:10 is expected by using a typical emulator or interpreter without caching [33]. With caching, it has ranged from 1:100 with the software simulators in the 1970s to 1:4 in 1990s [34].

Emulation is mainly used to address the cross-ISA problems between software and hardware. In the narrow sense of virtualization, however, the source and target ISAs are of the same, which permits simpler and more efficient ways for processor virtualization. Instead of the instruction interpretation and binary translation, efforts were made to execute the instructions of the source software directly on the target platform. As one of the primary targets for system virtualization, the "x86-based processor" has a few drawbacks in its ISA. This is because some instructions behave differently in virtual and physical environments. These include privileged instructions, behavior-sensitive instructions, as well as control-sensitive instructions [35].

According to the **classic virtualization condition**<sup>3</sup> proposed by Popek and Goldberg [14], x86-based ISA violates it, thus cannot be virtualized without additional efforts. Breakthrough is first achieved by VMware Workstation (a VMware type-2 hypervisor), which compensates the ISA drawbacks by a complex software functionality, the *dynamic binary translation* (DBT) [35]. By scanning and fixing the afore-mentioned three types of nocuous instructions at run-time, the

$<sup>^{2}</sup>$  code expansion is measured by the ratio of instructions in source ISA and target ISA, respectively.

<sup>&</sup>lt;sup>3</sup>**Theorem 1** For any conventional third-generation computer, an effective VMM may be constructed if the set of sensitive instructions for that computer is a subset of the set of privileged instructions.

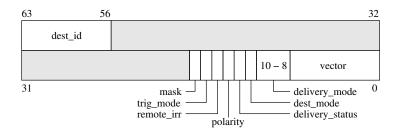

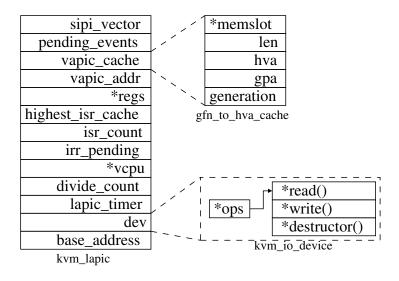

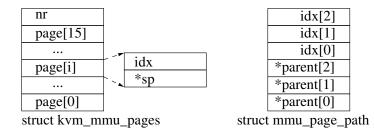

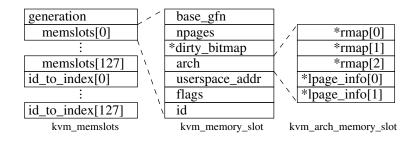

DBT lets the majority of source (guest) instructions directly run on the physical processor. Xen [36], a popular type-1 hypervisor, exploits paravirtualization [37] to overcome the drawbacks of x86-based ISA. The guest OS needs a slight modification to replace the nocuous instructions with the pre-defined secure routines (hypercalls) before execution. The paravirtualization occurs statically, thus yields higher performance and requires to access the source code of the guest OS.